一種基于ADSP-BF537的無線視頻傳輸方案

對DSP而言,DSP通過外部總線連接到SRAM0和SRAM1,這就相當于外擴了兩個外部RAM,DSP可以自由地訪問它們。圖2中的SRAM0,SRAM1分別用于DSP發送數據和接收數據。SRAM0和SRAM1本身是雙口RAM,可以供DSP和FPGA訪問,就是通過這種共享存儲器的方式完成數據交互。

2.3 軟件系統結構

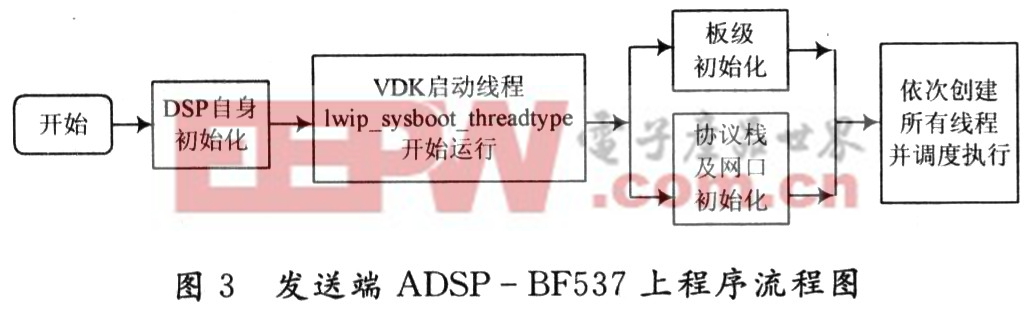

相關程序是用含有VDK(Visual DSP Kernel)的DSP軟件開發工具Visual DSP開發的。VDK是一種帶有API函數庫的實時操作系統內核,它具有任務調度和任務管理功能,一共支持32個任務。VDK是整個軟件的基礎,所有其他的程序都運行在該Kernel上。程序流程圖如圖3所示。

上電或復位后,DSP自啟動后VDK啟動線程lwip_sysboot_threadtype開始運行。在線程lwip_sysboot_threadtype中進行板級初始化和Lwip協議棧和網口初始化,其中板級初始化包括FPGA初始化,EBIU初始化,MDMA初始化,FLAG初始化。接下來創建下面幾個線程:

(1)數據傳輸:視頻數據傳輸。用于從編碼器獲取編碼后的視頻數據流,并存儲到緩沖區中。

(2)FPGA中斷:視頻數據發送中斷;MDMA中斷。

DSP首先通過Socket與視頻服務器連接,從視頻服務器獲取視頻數據,并將數據緩存后按照特定的格式打包,等待FPGA觸發視頻數據發送中斷。中斷觸發后,DSP啟動MDMA將一幀大小的數據發送給FPGA發送緩沖區。當MDMA操作完成后,觸發MDMA中斷,將幀頭寫入FPGA發送緩沖區的頭兩個字節。FPGA將接收的數據進行基帶算法處理后再將數據發送給射頻部分,之后FPGA再觸發視頻數據發送中斷,告訴DSP可以下一幀的發送,于是又啟動MDMA,如此循環。

3 實驗結果和分析

對系統在不同的信噪比的環境中傳輸的誤碼率進行了測試。測試方法如下:將發射機的輸出端口通過數據排線與邏輯分析儀相連,邏輯分析儀將采集到的一幀發射信號送到PC中用Matlab軟件對其加上噪聲,得到信噪比固定的信號。將這個信號導人信號源中進行不間斷循環發送給接收端的輸入端口。接收機接收信號進行解調并將解調出的數據傳給PC以統計誤碼率。測試結果如表2所示。

4 結 語

設計了一種無線視頻傳輸系統的方案,并對其中發射部分的數據通信過程做了詳細闡述。從硬件架構和軟件設計兩方面說明了數據在視頻服務器、DSP和FP-GA之間的傳遞過程。其中ADSP-BF537作控制器,成功完成了動態配置FPGA和通過網口傳送視頻數據的功能。該方案很好地滿足了大數據量,實時性的數據處理和結構靈活,模塊化設計相結合的要求。同時DSP+FPGA的數字硬件系統開發周期較短,系統容易維護和擴展,適合實時信號處理,使方案有更廣泛的應用。

評論