一種基于ADSP-BF537的無線視頻傳輸方案

無線通信技術和視頻壓縮技術的迅速發展,使得無線視頻傳輸成為人們研究的熱點。無線視頻傳輸具有數據量大,實時性要求高,無線信道資源有限的特點。新一代的視頻壓縮標準H.264結合專用視頻DSF芯片可以滿足信源編碼的要求。而處理數據量大,速度快,運算結構相對簡單的FPGA適用于信道編碼。基于以上考慮,設計了一個無線視頻傳輸系統,并以發射端ADSP-BF537作為控制器,配置FPGA和進行數據通信。

1 總體結構實現方案

系統硬件的實現方案如下:

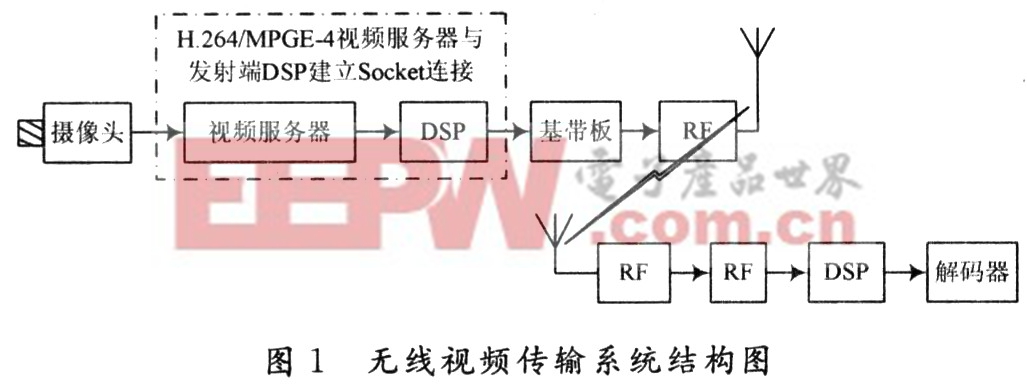

發送端由攝像機、專用視頻編碼芯片、控制模塊、基帶模塊、射頻模塊(RF)等部分組成。接收端由射頻接收模塊、控制模塊、基站模塊、專用視頻解碼芯片等部分組成。系統結構如圖1所示。

視頻編碼部分使用基于DM642的H.264視頻編碼器。該芯片通過網口傳輸數據,輸出的視頻流是H.264格式,輸出圖像的分辨率范圍為176×144~702×576,而且可以根據具體需要修改碼流和幀率。

控制模塊使用ADI公司的ADSP-BF537作為主要芯片。其主要作用是完成FPGA的配置、接口控制、通信鏈路的建立(視頻流數據的傳輸)。

基帶模塊以Xilinx公司Spartan3 400萬門級芯片的FPGA作為主要芯片。FPGA完成整個基帶信號處理,包括信道編碼、OFDM調制、濾波等。

射頻模塊由發射單元、接收單元、頻率合成單元、外置15 W功放等四部分組成,采用差分I,Q信號調制、解調,雙向傳輸。發射單元將I,Q差分輸入經調制芯片調制成340 MHz的射頻信號,經功率控制、功放、隔離器送往環行器、天線;通過收發電平控制進行發送和接收的切換;接收單元對接收信號進行濾波、低噪聲放大器后送I,Q解調芯片解調出差分的I,Q信號,并進行RSSI檢測和AGC控制。工作模式采用半雙工模式;頻率合成單元為發射單元提供340 MHz本振信號,為接收單元提供680 MHz本振信號。

2 控制模塊中DSP與FPGA數據通信

由于FPGA基于SRAM工藝,上電后數據會丟失。一般FPGA除了采用邊界掃描方式JTAG下載外,更多采用與FPGA相對應PROM芯片靜態配置,這種配置方式由于PROM容量小,價格昂貴,易于燒壞等缺點,在產品化之前一般不予采用,更可取的方法是采用控制器動態配置FPGA,比如單片機、DSP。同時,視頻服務器通過網口發送視頻數據,需要一個控制部分前向網口接收視頻服務器的數據,后向配置FPGA,發送視頻數據。基于以上考慮,整個系統中控制部分均由ADI公司的Blackfin系列DSP BF537完成,DSPBF537通過接口與視頻服務器和FPGA通信。

2.1 硬件平臺

ADSP是ADI(Analog Device Inc.)公司推出的一系列高性能低功耗DSP芯片,而基于Blackfin處理器的ADSP-BF537具有接口豐富,性能優良,價格低廉等特點,并具有強大的多媒體數據處理能力。Blackfin處理器集成了一個由ADI公司和Intel公司聯合開發的基于MSA(Micro Signal Architecture)的16/32位嵌入式處理器,支持32位RISC指令集,采用10級流水線,集成了兩個16位乘法加速器,內核主頻最高可以達到600 MHz。ADSF-BF537總線有一個以DMA控制器為中心的高速自主數據通道。DMA總線可以在存儲器之間、存儲器和外部接口之間快速地傳遞數據,并且可以和內核并行操作。ADSP的集成開發環境Visual DSP++中嵌入了實時操作系統內核VDK,適合多任務多線程的嵌入式操作。ADI還提供了一個用于Blackfin系列嵌入式處理器的輕量級TCP/IP(LwIP)協議棧端口,可以快速將一個獨立的嵌入式應用聯網。

2.2 硬件系統架構

DSP與視頻服務器采用輕量級TCP/IP(LwIP)交互數據,這里不過多介紹。主要介紹DSP與FPGA連接。由于FPGA基于SRAM工藝,掉電后數據會丟失。采用的方法是將作用于FPGA的通信基帶算法文件存儲在DSP的FLASH中。一般調試時,DSP及FPGA都需要從PC機通過JTAG口進行程序的下載。但當系統程序已經調試完畢,當需要到戶外進行測試或作為產品使用時,針對系統調試的方便性,采用DSP自啟動及配置FPGA部分。

ADI公司的ADSP-BF537上電后啟動方式一共有7種。本設計中采用的DSP上電從16位FLASH啟動,啟動程序采用Analog公司提供的燒寫啟動FLASH的程序。第一次上電時,利用JTAG,結合ADSP自帶工具“FLASH Programmer”將寫好的DSP程序燒入FLASH中。并且將FPGA的配置文件(.bit格式)讀到緩存,通過DSP燒寫到FLASH的Bankl和Bank2中,把Bank0用來做DSP自啟動。斷電復位后,啟動過程如下:

(1)BF537從FLASH引導啟動,完成DSP板級初始化。

(2)FPGA的配置文件動態加載到FPGA中。

(3)用DSP的GPIO端口對FPGA的時鐘和數據配置專用引腳進行模擬時序,即完成對FPGA的動態配置。

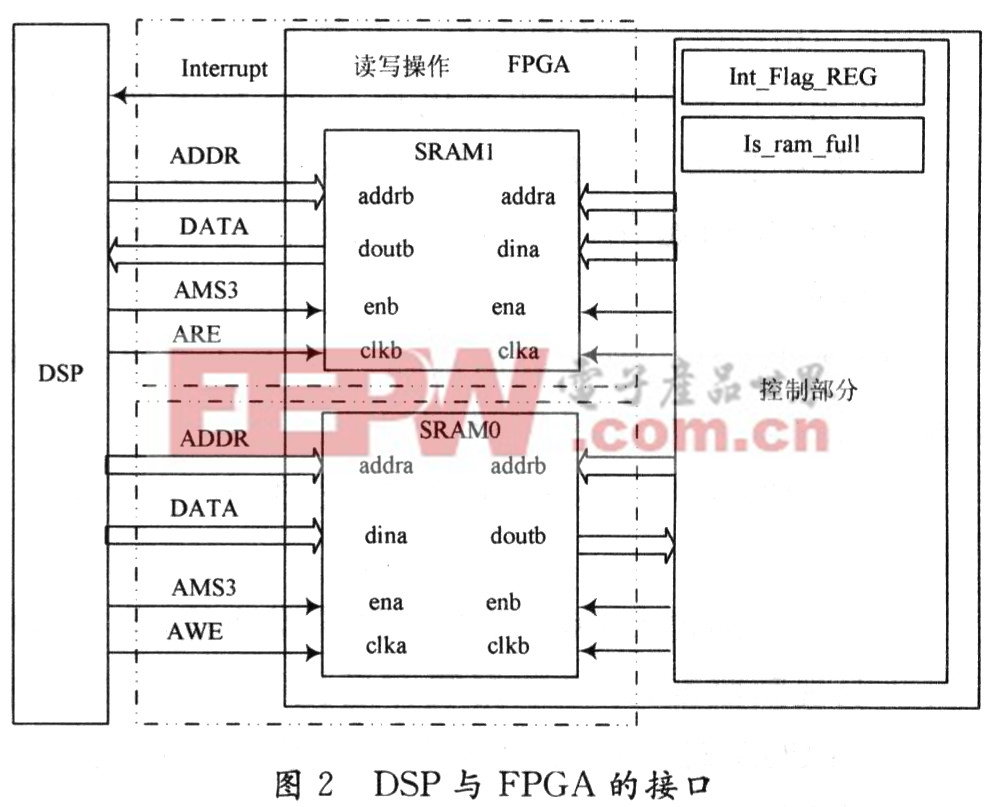

在啟動過程完成后,DSP與視頻服務器進行Sock-et連接,接收壓縮的視頻碼流,并送到FPGA進行基帶部分的處理。DSP與FPGA的接口部分如圖2所示。

評論