一種數字射頻存儲器的設計

由于有斜視角引起多普勒中心不為零,對方位時域數據作相位補償,補償的相位函數是:本文引用地址:http://www.104case.com/article/157923.htm

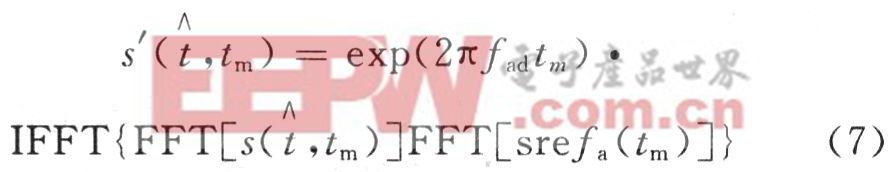

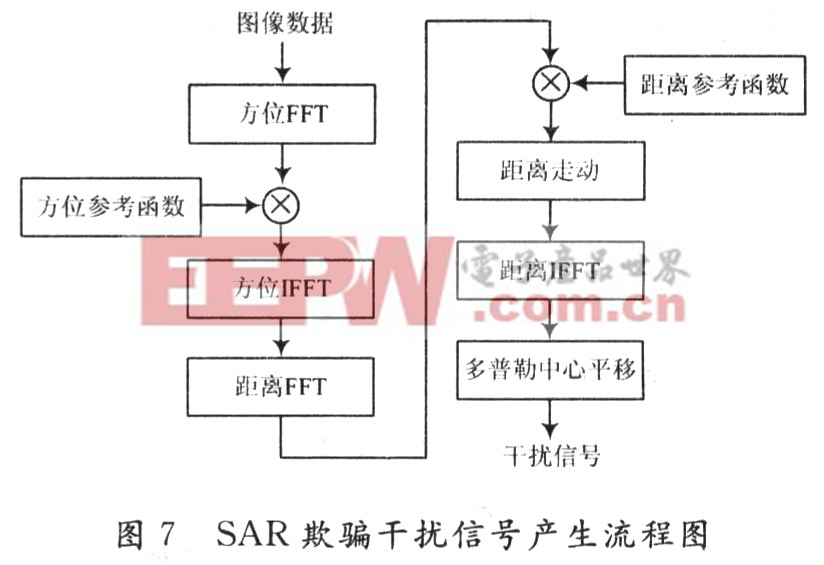

方位向欺騙干擾的實現是對方位向信號進行卷積處理,即:

經過二維卷積處理之后,可獲得對應場景的干擾信號s′(t,tm)。

4 硬件設計注意事項

整個DRFM模塊工作的頻率很高,設計時應該嚴格按照高速電路的設計原則處理每一個細節。

4.1 時鐘的設計

時鐘電路設計的好壞直接影響高速電路的工作性能。為了防止高速時鐘受到外界干擾或向外輻射干擾,需要把時鐘的電源和地與其他的電源、地分開。差分信號可以有效的防止干擾,把送入的時鐘轉換為差分的LVDS或ECL等電平后再使用,可以有效提高時鐘質量。板上送到不同地方而又有相位要求的兩個時鐘,例如送到兩路ADC的時鐘,走線要等長,并控制好阻抗。

4.2 電源和地的噪聲

在高速電路中30%以上的噪聲來自電源和地。對于一個印制板,電源、地和過孔構成了整個電源分布系統。板上的大量器件同時開關時需要較大的瞬時電流,這將會帶來電源和地的波動,從而引入干擾。去耦是解決電源地噪聲的有效方法,把合適的電容放置在器件的管腿附近進行濾波,可以提高電源穩定性。如果板上空間允許,可以放置盡量多的電容。該系統中的高速數據采集和光纖接口板采用光纖傳輸方式,光纖傳輸速率高,對電源比較敏感,需單獨用穩壓塊提供供電,和其他3.3 V電分開。

4.3 信號的走線

關鍵信號盡量走在頂層或底層,這樣容易控制阻抗并且可以避免過孔影響信號完整性。需要時用地線包住信號線,屏蔽干擾。過孔之間避免太近,容易引起互擾。盡量使同一層面信號線網的參考層面為地層,切勿以主要層面為電源層。

5 結 語

主要介紹了DRFM的硬件實現。其高速數據采集和寬帶波形產生保證了系統的大瞬時帶寬,6塊并行DSP處理板使得系統具有極強的信息處理能力,便于相干干擾、噪聲壓制干擾等不同干擾樣式的產生。大的存儲容量使得系統可以保存脈寬很寬的樣本信息。鑒于該DRFM由三部分組成,體積較大,數據中間傳輸過程較多。以后設計應該考慮模塊化,小型化,方便調試。該設計已成功運用在某型號產品上,事實證明了其可靠性和穩定性。

評論