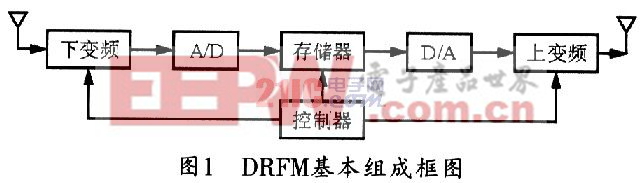

基于MAXl01A的1GHz數字射頻存儲器的設計與實現

2 DRFM數據采集模塊的設計

2.1 MAXlOlA的主要特點

ADC芯片是數據采集的核心器件,本系統中A/D轉換器采用MAXIM公司的MAXlOlA,它的最高采樣速率可達到500 Msps,采樣精度為8 bit。本文采用兩片MAXl01A交替采樣,以使系統達到1 Gsps的采樣速率。MAXlOlA主要特點如下:

◇具有500 MHz轉換速率;

◇在250 MHz時的有效位為7.0位;

◇1.2 GHz模擬輸入帶寬;

◇誤差小于±1/2LSB INL;

◇帶50 Ω差分或單端輸入;

◇具有±250 mV的模擬輸入范圍;

◇數據通路可雙路鎖存輸出;

2.2 MAXl01A的原理

(1)多位轉換

MAXl01A采用并行結構(即閃爍結構)進行比普通積分ADC更快的多位轉換。典型的n位閃爍結構含有(2n-1)個比較器,其負輸入端均勻的從基準網絡階梯電阻的底部排布到頂部,各占據一個LSB增量值。MAXl01A是一個單片雙交叉并行量化的芯片,它內部具有兩個獨立的8位轉換器,n=8時,應有255個比較器。這些轉換器將結果傳送給A、B兩組輸出端,并在輸入時鐘交替負邊沿鎖存它們。

(2)跟蹤/保持

MAXlOlA內部自帶的跟蹤/保持放大器提升了獲得有效數據位的性能,并允許在高轉換速率情況下仍以較高的精度捕捉模擬數據。其內部

Track/Hold電路為MAXIMA提供了兩個重要的功能:一是它的4倍額定增益減少了輸入差動電壓的振幅,對±1.02 V基準源,輸入信號為+250

mV;二是提供一個差動的50 Ω輸入,使MAXl01A接口應用極為方便。

(3)數據流

MAXlOlA內部的跟蹤/保持放大器為ADC提供模擬輸入電壓的采樣。而T/H放大器被同時分為兩部分,分別工作在交替的時鐘負邊沿。輸入時鐘CLK應滿足T/H放大器要求,同時還可回饋給A/D部分。輸出時鐘DCLK用于數據定時,是輸入時鐘CLK的2分頻或10分頻。

2.3 MAXlOlA的應用

(1)模擬輸入范圍

雖然正常工作范圍為+250 mV,但對MAXl01A的每個輸入端而言,其對地的輸入范圍實際上為±500 mV,這擴展了包括模擬信號和任何DC共模的電壓的輸入電平。要在差動輸入模式下得到滿量程的數字輸出,應在AIN+和AIN-之間加+250 mv電壓,也就是說,AIN+=+125 mV,AIN-=-125mV (無直流偏置)。在模擬輸入端之間無電壓差時,會出現中間刻度數字分驅動為-250mV,即AIN+=-125 mV,AIN-=+125 mV時,會出現零刻度數字輸出代碼。

(2)基準

ADC的基準電阻確定了ADC的最低有效位(LSB)的大小和動態工作范圍。通常,電阻串的底部和頂部都是由內部緩沖放大器驅動的。在ADC的基準輸入端加RC網絡可獲得最佳性能,可將一個33 Ω電阻與驅動該基準電阻串的緩沖輸出級相聯,而0.47μF電容必須接在緩沖輸出級的電阻器旁邊。這個電阻與電容的組合必須位于MAXl01A封裝的0.5英寸(1.27 cm)之內。任一端接點的噪聲都會直接影響代碼的檢測,并且降低ADC的有效數據位指標。

評論