功率LDM0 S中的場極板設計

摘要:本文提出了LDMOS器件漂移區(qū)電場分布和電勢分布的二維解析模型,并在此基礎上得出了LDMOS漂移區(qū)電勢分布和電場分布的解析表達式。通過表達式的結果,研究了多晶硅場板的長度和位置對于器件表面電場和電勢的影響,解析結果與MEDICI結果相符。

關鍵詞:橫向擴散金屬氧化物半導體;多晶硅場板;表面電場;表面電勢

0 引言

隨著功率集成電路的飛速發(fā)展,功率半導體器件的研究與開發(fā)顯得愈發(fā)重要。LDMOS是DMOS器件的一種橫向高壓器件。具有耐壓高、增益大、失真低等優(yōu)點,并且更易與CMOS工藝兼容,因此在射頻集成電路中得到了廣泛的應用。目前LDMOS設計的重點是如何合理緩和擊穿電壓與導通電阻之間的矛盾,并且保證其有較高的穩(wěn)定性。

場板技術是功率LDMOS器件中使用最為頻繁的一種終端技術。合理的場板設計可以使漂移區(qū)的平均電場增加,減小電場峰值,從而達到抑制熱載流子效應,提高擊穿電壓等目的。因此,建立LDMOS的電場分布模型,理論上對場板下的電場分布進行數值分析有重要的現實指導意義。本文將通過建立二維解析模型研究LDMOS的場板的不同結構對于其漂移區(qū)電場和電勢的影響,并在此基礎上通過優(yōu)化場板來提高LDMOS的性能。

1 二維解析模型

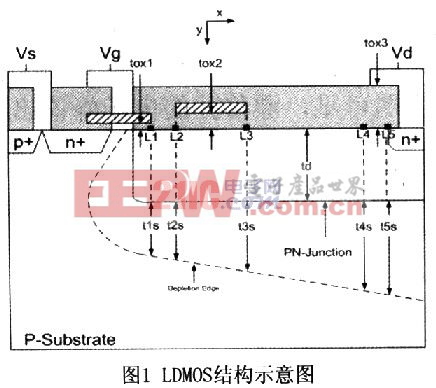

LDMOS的橫向切面圖如圖l所示。其中X和Y分別為距漂移區(qū)左上角的橫向距離和縱向距離,漂移區(qū)分成五部分,各區(qū)邊界點的橫坐標分別設為L1、L2、L3、L4和L5。各區(qū)對應的襯底耗盡層寬度分別為tis(i=1,2,3,4,5)。柵極下氧化層的厚度為tox1,場板下的氧化層厚度為tox2,漏端下氧化層厚度為tox3。n-drift漂移區(qū)的濃度為Nn,厚度為td。P型硅襯底濃度為Nsub,所加柵壓為Vg1,場板所加電壓為Vg2,漏壓Vd。源極和襯底接地。則漂移區(qū)的二維電勢分布φ(x,y)滿足二維泊松方程:

其中εo和εsi分別為真空介電常數和Si的介電常數。

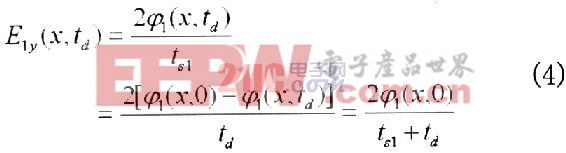

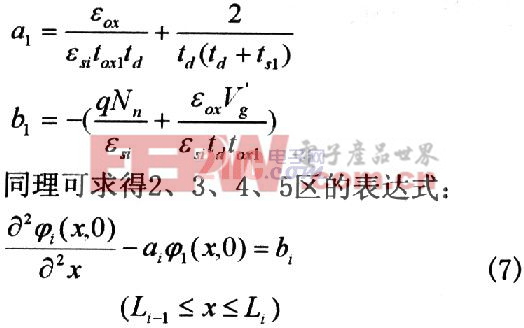

由于漂移區(qū)是均勻摻雜的,在1區(qū)(0≤x≤L1)對式(1)進行y方向的積分可得:

由于Si02/Si界面上的電位移是連續(xù)的,忽略Si02中固定電荷,可得:

評論