異步FIFO在FPGA與DSP通信中的運(yùn)用

2 DSP端數(shù)據(jù)接收

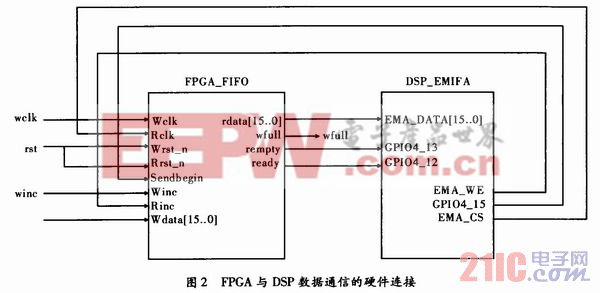

TI公司的TMS320C6000系列DSP均提供EMIFA接口,本文利用EMIFA接口實(shí)現(xiàn)FPGA向DSP傳輸數(shù)據(jù),實(shí)現(xiàn)兩者硬件連接的電路如圖2所示。本文引用地址:http://www.104case.com/article/156394.htm

其中,EMIFA的16位數(shù)據(jù)端與FIFO的Rdata端相連以便接收FPGA發(fā)來的數(shù)據(jù),GPI04_13,GPI04_12,GPI04_15這3個(gè)通用IO口用來接收或輸出相應(yīng)的握手信號。EMA_WE與FIFO的讀使能端相連,EMA_CS與FIFO的讀時(shí)鐘相連。

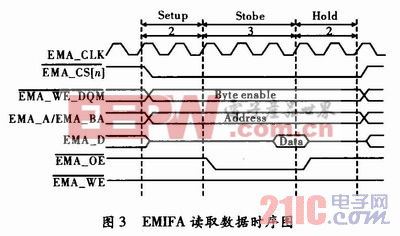

圖3所示為DSP的EMIFA口讀取數(shù)據(jù)的時(shí)序圖,從圖中可以看出,每一次讀數(shù)據(jù)操作均以EMA_CS(EMIFA使能信號)下降沿開始,以EMA_CS的上升沿結(jié)束。同時(shí),因?yàn)槭亲x取操作,EMA_WE(EMA讀寫控制信號,低為寫,高為讀)始終為高電平,EMA_OE(EMA輸出使能信號,低有效)在數(shù)據(jù)讀取時(shí)刻為低電平。所以,將EMA_CS連至FIFO的Rclk端,恰好實(shí)現(xiàn)DSP讀取一次數(shù)據(jù),F(xiàn)IFO更新一個(gè)數(shù)據(jù),而EMA_WE可作為FIFO的讀使能信號。

3 仿真結(jié)果與結(jié)論

本文設(shè)計(jì)了數(shù)據(jù)寬度為16位,深度為2 048的FIFO,并使用Verilog語言編寫了FIFO模塊和與DSP的接口模塊,利用該FIFO,FPGA實(shí)現(xiàn)了將數(shù)據(jù)1~65 535傳遞給DSP。在Quartus II軟件下進(jìn)行仿真得到的結(jié)果如圖4所示。

由圖4可以看出,在rst變?yōu)楦唠娖揭院螅現(xiàn)PGA在Wclk的上升沿依次將數(shù)據(jù)寫入FIFO中,寫指針也從0開始逐次增1。在收到DSP發(fā)來的gp15(啟動(dòng)數(shù)據(jù)發(fā)送信號)有效后,在讀時(shí)鐘Rclk的上升沿,F(xiàn)PGA將數(shù)據(jù)從1開始逐次輸出到Rada端,供DSP讀取。DSP端在配置好EMIFA口后,編寫的相應(yīng)接收程序,正確接收到了從0~65 535這65 536個(gè)數(shù)據(jù)。

為實(shí)現(xiàn)FPGA與DSP之間的數(shù)據(jù)通信,本文提出了利用異步FIFO的方法,采用格雷碼和兩級D觸發(fā)器同步的方法降低了亞穩(wěn)態(tài)現(xiàn)象出現(xiàn)的概率。同時(shí),給出了FPGA和DSP實(shí)現(xiàn)數(shù)據(jù)通信的硬件連接電路。經(jīng)驗(yàn)證,利用異步FIFO的方法,能夠穩(wěn)定可靠地從FPGA中傳輸數(shù)據(jù)給DSP。

評論