基于Verilog HDL濾波器的設計

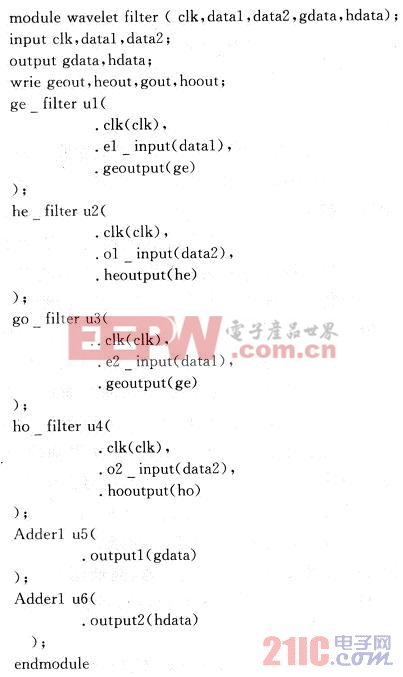

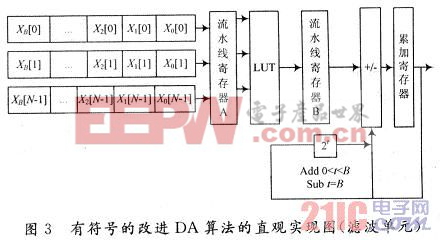

對于雙正交小波濾波器的部件Ge,Go,He,Ho設計,采用行為描述方式進行設計。VerilogHDL行為描述語言作為一種結構化和過程性的語言,其語法結構非常適合于算法級和RTL級的模型設計。在Veril—ogHDL語言中行為描述分為算法和RTL兩種。算法級:用語言提供的高級結構能夠實現算法的運行模型。RTL級:描述數據在寄存器之間的流動和如何處理,控制這些數據的流動,采用改進的DA算法(如圖3所示)。DA算法完成一次濾波所需要B次的累加也就是B個時鐘周期完成一次運算,B位輸入數據的位寬。它的查找表(LUT)的大小是由濾波器的階數N決定的,共需要2N個查找表單元,如果系數N過多,用單個LUT不能夠執行全字查找則可把系數分組,利用部分表并將結果相加,為了簡單的闡述算法,在此系數只分了2組,每個單元的位寬是由濾波器的系數的量化決定的。Ge,Go,He,Ho四個濾波器雖然長度不同,但具有相同的電路結構,如圖4所示。

評論