基于SOPC技術(shù)的異步串行通信IP核的設(shè)計(jì)與實(shí)現(xiàn)

3. 3.1 波特率模塊

波特率模塊根據(jù)PLB總線提供的時(shí)鐘產(chǎn)生需要的發(fā)送時(shí)鐘和接收時(shí)鐘。由于UABT在發(fā)送數(shù)據(jù)時(shí)只需要按照發(fā)送波特率將數(shù)據(jù)串行地發(fā)出就可以了,因此發(fā)送時(shí)鐘就等于發(fā)送波特率。而當(dāng)UART在接收數(shù)據(jù)時(shí),需要對串行數(shù)據(jù)進(jìn)行采樣以判斷接收數(shù)據(jù)。由于接收方和發(fā)送方的時(shí)鐘不可能完全同步,所以需要對每一位接收數(shù)據(jù)持續(xù)電平的時(shí)間進(jìn)行分段。分段越多,接收出現(xiàn)誤判的概率就越低,但系統(tǒng)開銷也越大。在實(shí)際的設(shè)計(jì)中通常采用發(fā)送時(shí)鐘的16倍作為接收時(shí)鐘。波特率模塊的分頻功能由兩個(gè)16位計(jì)數(shù)器實(shí)現(xiàn),它將PLB總線時(shí)鐘按配置寄存器的設(shè)定進(jìn)行分頻,產(chǎn)生發(fā)送時(shí)鐘和接收時(shí)鐘。

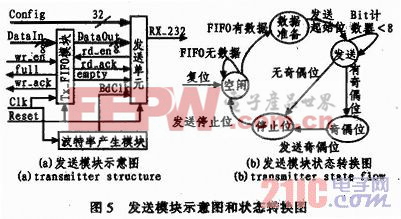

3.3.2 發(fā)送模塊

發(fā)送模塊主要包括發(fā)送FIFO和發(fā)送單元兩部分,如圖5(a)所示。發(fā)送FIFO數(shù)據(jù)位寬度為8bit,深度為16字節(jié)。發(fā)送FIFO緩存MicroBlaze處理器需要發(fā)送的數(shù)據(jù)。當(dāng)FIFO空間滿時(shí),發(fā)送模塊將狀態(tài)寄存器中“發(fā)送FIFO滿”標(biāo)志位置1,MicroBlaze處理器通過查詢該位以判斷UART IP核是否可以接收下一個(gè)發(fā)送數(shù)據(jù)。本文引用地址:http://www.104case.com/article/154802.htm

發(fā)送單元的設(shè)計(jì)用有限狀態(tài)機(jī)的方法實(shí)現(xiàn),其狀態(tài)轉(zhuǎn)換圖如圖5(b)所示。系統(tǒng)在復(fù)位后,發(fā)送單元處于空閑狀態(tài)。當(dāng)FIFO有發(fā)送數(shù)據(jù)時(shí)(Empty管腳為低),發(fā)送單元發(fā)出讀FIFO操作,并進(jìn)入數(shù)據(jù)準(zhǔn)備狀態(tài)。當(dāng)數(shù)據(jù)從FIFO中讀出,發(fā)送單元首先發(fā)送起始位,進(jìn)入發(fā)送狀態(tài)。在發(fā)送狀態(tài)下,發(fā)送單元依次串行發(fā)送8比特?cái)?shù)據(jù),并計(jì)算當(dāng)前的奇偶校驗(yàn)碼。在數(shù)據(jù)發(fā)送結(jié)束后,若配置寄存器中奇偶校驗(yàn)位為1,則發(fā)送奇偶校驗(yàn)位。最后發(fā)送單元發(fā)送停止位,回到空閑狀態(tài),完成次數(shù)據(jù)發(fā)送。

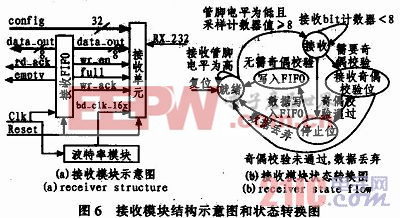

3.3.3 接收模塊

接收模塊由接收FIFO和接收單元兩部分組成,如圖6(a)所示。接收FIFO數(shù)據(jù)位寬度為8bit,深度16字節(jié),它負(fù)責(zé)緩存接收單元收到的數(shù)據(jù),并在收到數(shù)據(jù)后將狀態(tài)寄存器中“接收數(shù)據(jù)有效”標(biāo)志位置1。MicroBlaze處理器通過查詢該位來判斷是否有數(shù)據(jù)到達(dá)。

接收單元的設(shè)計(jì)同樣采用了有限狀態(tài)機(jī)的方法,其狀態(tài)轉(zhuǎn)換圖如圖6(b)所示。系統(tǒng)在復(fù)位后接收單元處于就緒狀態(tài)。當(dāng)接收單元在接收管腳連續(xù)檢測到8個(gè)低電平時(shí)認(rèn)為起始位有效,進(jìn)入接收狀態(tài)。在接收狀態(tài)下,接收單元每16個(gè)接收時(shí)鐘采集一次接收數(shù)據(jù)。8個(gè)接收數(shù)據(jù)都采集完成后,接收單元根據(jù)配置寄存器中“奇偶校驗(yàn)位”是否為1決定是否進(jìn)行奇偶校驗(yàn)。若奇偶校驗(yàn)通過,接收單元將接收到的數(shù)據(jù)寫入接收FIFO。若奇偶校驗(yàn)未通過接收FIFO滿,接收單元丟棄收到的數(shù)據(jù),并在狀態(tài)寄存器中置“奇偶校驗(yàn)出錯(cuò)”位或“接收FIFO滿”位為1。

4 實(shí)驗(yàn)驗(yàn)證

4. 1 系統(tǒng)硬件介紹

本文采用Xilinx公司提供的ML505 V5 FPGA Demo板作為SoPC系統(tǒng)硬件平臺。ML505 FPGA演示驗(yàn)證板主要由一塊Virtex-5 XC5VLX50T FPGA構(gòu)成,此外還包括RAM、Flash、以太網(wǎng)接口芯片、USB接口芯片以及ADM3202 RS-232電平轉(zhuǎn)換芯片等外圍擴(kuò)展芯片,其中ADM3202電路原理圖如圖7所示。

實(shí)驗(yàn)采用Xilinx公司ISE工具完成UART IP核的邏輯綜合和仿真,仿真波形如圖8所示,發(fā)送數(shù)據(jù)為0x01。

評論