基于FPGA的通信接口模塊設計與實現

協議使用8B/10B編碼保證數據通道的直流平衡,完成時鐘的恢復。同時利用8B/10B編碼的控制字符作為數據幀傳輸的起始、結束標識,并作為傳輸信道的同步控制。在每一數據幀的起始位置添加幀起始控制字符,在數據幀的結束位置添加幀結束控制字符,在數據傳輸過程中有中斷或在無數據傳輸的空閑時段填充同步控制字符。本文引用地址:http://www.104case.com/article/154067.htm

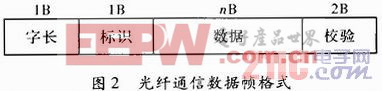

控制命令和狀態數據都以數據幀的方式在光纖上傳輸。數據幀格式如圖2所示。標識字說明數據幀的性質和傳輸到的設備,不同的應用有不同的標識,且每個標識有唯一對應的設備,一個設備可能有多個標識字。字長為從標識到校驗的長度。數據為命令或狀態信息。校驗字為從字長到數據的所有字節的循環冗余校驗碼(CRC)。

2 通信接口模塊實現

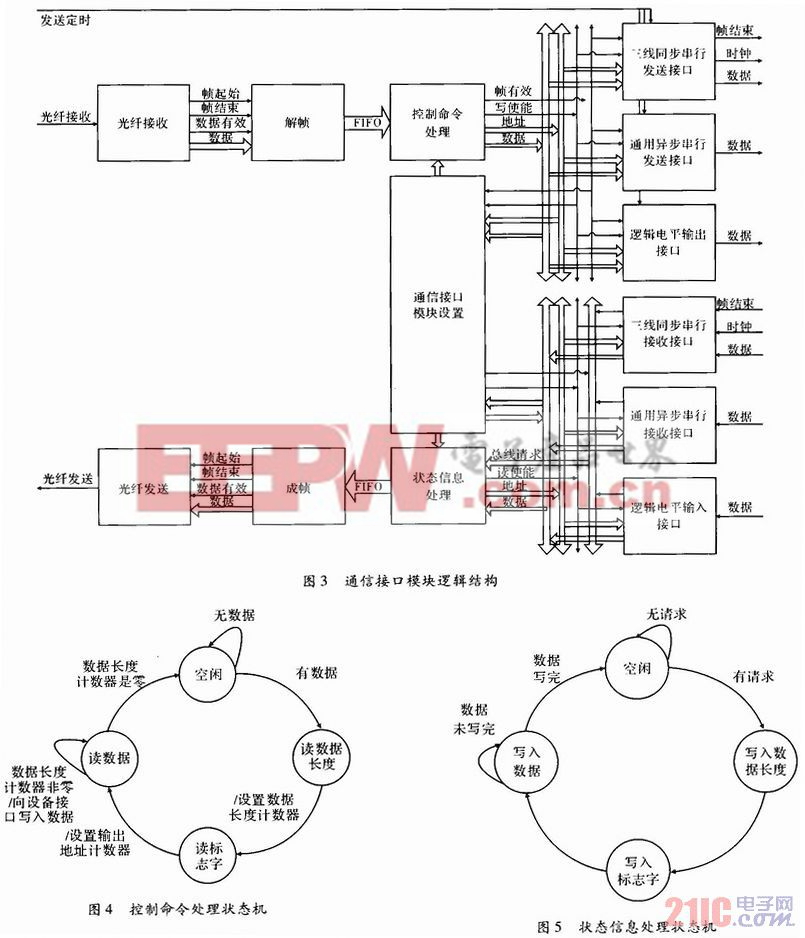

通信接口模塊以FPGA為控制核心,外圍添加電平轉換芯片實現。通信接口模塊對上行控制命令和下行狀態信息進行獨立處理。在FPGA內實現的邏輯框圖如圖3所示。

光纖接收和光纖發送模塊實現光纖通信協議的物理層處理。成幀和解幀模塊實現光纖通信協議的鏈路層處理。控制命令處理和狀態數據處理實現用戶數據處理。三線同步串行接口、通用異步串行接口和邏輯電平接口實現針對各個前端受控模塊的數據傳輸。

2.1 光纖接口

按照光纖通信協議,光纖接口包括物理層和鏈路層處理,即圖3中的光纖發送/接收、成幀/解幀邏輯模塊,發送和接收是相反方向的處理。光纖接收/發送邏輯模塊實現串行解串編解碼和8B/10B編解碼。串行器將并行數據變為串行數據發送至光纖接口;解串器將從光纖接口接收到的串行數據變為并行數據。同時通過8B/10B編碼將發送時鐘編碼到數據中一同發送,解串器則從數據流中恢復時鐘。串行器采用

SN65LV1023A器件,解串器采用SN65LV1224B器件。8B/10B編解碼則在FPGA中實現。成幀/解幀模塊實現數據長度檢驗、數據校驗、添加幀頭和幀尾。

2.2 控制命令處理邏輯

控制命令處理邏輯首先檢測FIFO緩沖器是否有數據,如有數據則開啟一次控制命令處理。數據處理時,根據標志字將數據寫入相應的設備接口,一幀數據處理完成后,通過設置幀有效信號,啟動接口模塊發送。控制狀態機如圖4所示。

評論