雙口RAM在組合導航系統中的應用

1.3 令牌判優方式

令牌判優方式是一種快速數據交換方式。在此方式中有信令鎖存邏輯,CY7C028內部提供了八個相互獨立的鎖存邏輯單元,最多可將RAM空間分成八個區段。這些鎖存邏輯單元獨立于雙口RAM存儲區,并不能控制RAM區、封鎖兩端CPU的讀/寫操作,而是被作為信令,只提供指示邏輯,由兩端CPU按約定的規則,輪流地占用它們劃定的RAM區,各區的大小及地址由軟件自由設定,且左右端操作完全一樣,只要不超過令牌的限制次數即可。當左右端口同時申請同一令牌時,令牌邏輯將裁定誰先占用,從而保證只有一個端口獲取令牌。而在占用令牌期間,CPU可以按最高速無等待存取數據,這對實現高速、多CPU數據采集與處理系統無疑是非常有利的。但是,為了避免令牌方式爭用出錯,應盡可能使兩端CPU分時占用同一RAM區。

2 雙口RAM在組合導航系統中的應用

2.1 系統總體設計

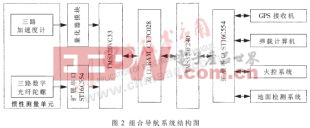

導航系統的主要任務是測量飛行載體的即時位置、速度、航向等導航參數,具有實時性高、運算量大等特點。因此在導航系統中,計算機設計是系統設計的關鍵之一。在INS/GPS組合導航系統中,導航計算機的任務主要有三類[6]:

(1) 數據采集,包括采集慣性測量單元元件輸出信號,接收外部系統校正信息,如GPS輸出信息、初始位置信息等。

(2) 數據處理與運算,包括慣性測量元件的誤差補償、初始對準、導航參數解算、組合導航算法實現等。

(3) 輸出導航數據及系統狀態量,包括輸出導航參數以及與其它設備交換信息等。

所有這些任務,如果都由一個CPU來完成,那么CPU在進行運算的同時,還要兼顧系統控制和數據輸入輸出,并響應頻繁的中斷,必然降低系統運行效率。所以,為了兼顧系統運行效率,減輕導航計算機負擔,設計一種以TMS320VC33為主機和以TMS320F240為接口機的雙DSP主從式系統。系統總體結構如圖2所示。

本文引用地址:http://www.104case.com/article/152579.htm

本文引用地址:http://www.104case.com/article/152579.htm主機TMS320VC33主要用來定時采樣陀螺、加速度計的數據,并完成姿態陣計算、組合系統卡爾曼濾波器計算等導航解算。接口機TMS320F240主要完成系統相關狀態的檢測/控制,與GPS接收機、彈載計算機及其它外設的通信等任務。主機和接口機之間的通信利用雙口RAM CY7C028實現。量化器模塊主要是將加速度計輸出的電流信號轉換成主機可直接讀取的數字量。此外,由于TMS320VC33和TMS320F240的串口資源有限,無法滿足系統需要,系統中采用EXAR公司的ST16C554進行相應的串口擴展。

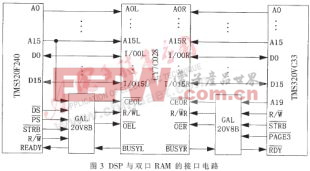

2.2 DSP與雙口RAM的接口設計

在組合導航系統中,CY7C028與兩個DSP芯片TMS320VC33和TMS320F240之間的接口電路如圖3所示[2~4]。TMS320VC33的數據線寬度為32位,而CY7C028的數據位寬為16位,因此采用將TMS320VC33數據總線的低16位與雙口RAM的數據總線相連。TMS320VC33在發送32位的數據至雙口RAM時,分兩次完成,先寫低16位,再寫高16位。從雙口RAM讀取數據操作與發送類似。如前所述,使用雙口RAM的關鍵是解決左右端口同時操作同一RAM單元的競爭問題。圖3中采用了硬件判優的方法,即將左右端口的BUSY信號經相應處理后分別引至支持插入等待時序的TMS320VC33和TMS320F240 的對應引腳,以解決左右端口對同一單元的爭用問題。

為了使整個系統成為完全可編程系統,增加系統的靈活性,系統中邏輯控制選用可編程的邏輯器件GAL實現[5]。GAL選用Lattice公司的GAL20V8B芯片,并采用Lattice公司提供的ispDesignEXPERT集成開發軟件對其進行邏輯編程。ispDesignEXPERT支持多種硬件編程語言,系統中采用ABEL語言進行編程。左、右兩端GAL的輸入管腳信號定義如圖3中所示。

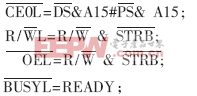

左端譯碼電路的邏輯方程為:

評論