基于ARM和FPGA的嵌入式高速圖像采集存儲系統

2.2 FPGA模塊

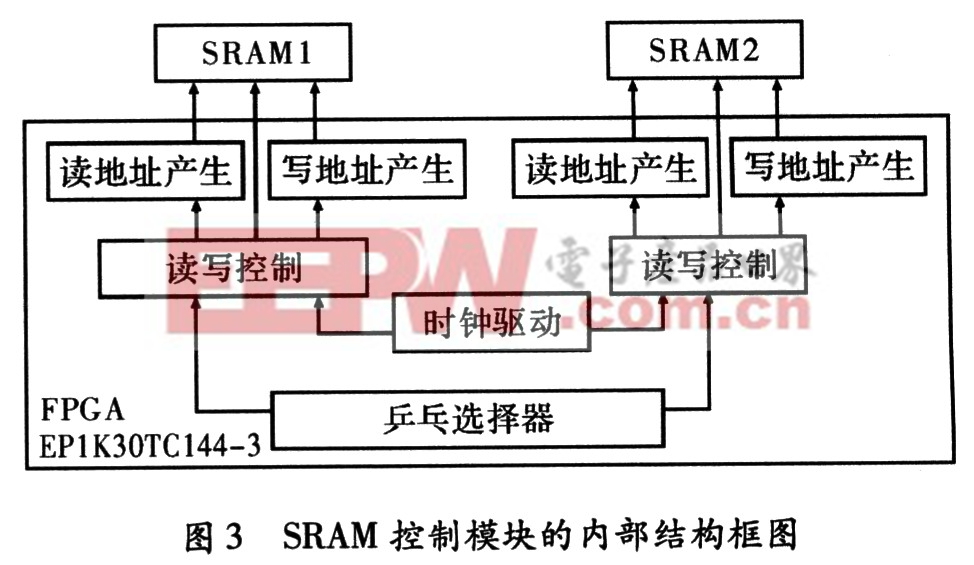

FPGA主要作用是把圖像采集芯片傳過來的圖像原始數據,采取乒乓操作的方式,暫存于兩片SRAM中。當FPGA開始接收第一幀圖像時,把該幀圖像根據FPGA內部生成的地址存儲在SRAMl中,一幀圖像接收完畢后,向ARM傳送。同時,把下一幀圖像暫存于SRAM2中,然后傳給ARM,依次循環。這樣就可以實現圖像的高速采集。本系統選用了Alter公司的EPlK30TCl44―3,它采用EECMOS技術,144引腳TQFP封裝,容量為10萬門,具有高密度、低成本、低功耗的特點。FPGA的內部結構包括時鐘驅動模塊、SAA7113H控制模塊、SRAM控制模塊、ARM數據交換模塊等。SAA7113H控制模塊主要負責對視頻采集芯片SAA7113H的初始化和啟停等功能控制;SRAM控制模塊則主要進行讀寫地址生成、“乒乓”讀寫控制等;ARM數據交換模塊負責向ARM申請中斷和數據傳輸。這些模塊在設計中利用VHDL語言,在Quartus II環境下進行編程和調試,具體實現方法參見文獻。本系統中,主要針對640×480的灰度圖像的采集和存儲,所以選用了ISSI公司的IS6lIN25616AL,它是一種高速度、低功耗的256 kB×16的CMOS靜態隨即存儲器,能夠滿足系統的實際要求。SRAM控制模塊的內部結構框圖,如圖3所示。本文引用地址:http://www.104case.com/article/152552.htm

2.3 ARM模塊

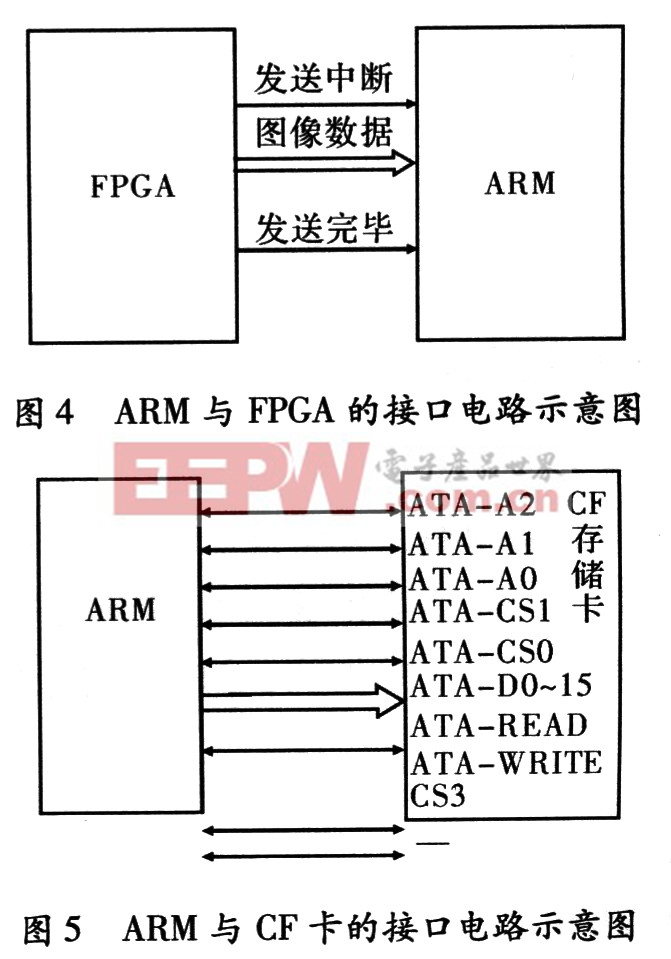

ARM模塊的主要作用是,從SRAM中取出圖像原始數據,然后進行必要的處理,再存儲在大容量的CF卡上,方便用戶在PC機上對圖像進行必要的處理操作。FPGA接收完一幀圖像后,向ARM發出中斷請求,ARM收到請求后,通過FP―GA將SRAM中的數據讀入。一幀數據發送完畢后,FPGA發出發送完畢信號,ARM對接收到的數據進行必要的處理后,將數據存儲在大容量的CF卡上。本系統選用了Philips公司的LPC2214,它是基于ARM7TDSI體系的嵌入式微處理器,內部具有16 kB的靜態隨機存儲器和256 kB的Flash程序存儲器,可實現高達60 MHz的工作頻率。ARM與FPGA及CF卡的接口電路分別,如圖4,圖5所示。

評論