基于DSP和FPGA的磁浮列車同步485通信方式的研究

2) ANF信號的產生:ANF信號每隔20ms發送一次,每次發送脈寬為10個時鐘周期。ANF信號的產生可以分成兩部分實現,首先產生每隔20ms的脈沖信號,然后把此脈沖信號的寬度變成10個時鐘周期。

(2)串行數據的發送與接收

1) 串行數據的產生:根據通信協議的要求,測速定位單元每隔20ms應串行移出72bits數據。如果每個發送時鐘周期移出一位,則需要72個時鐘周期才能全部移出,因此門控信號也需要保持72個時鐘周期的寬度。

2) 串行數據的接收:同步串行接收一幀(72bits)數據與異步串行接收是不同的。由于收發時鐘不是異步的,因此不能以判斷在空閑態以后出現的第一個低電平作為一幀的開始,而是以門控信號(UEF)的上升沿作為一幀數據到來的判斷。為了避免數據傳輸過程中毛刺的影響,仍以波特率時鐘的16倍進行接收,即每隔16個波特率時鐘周期采樣一次,因此每個數據將在傳輸的每一位的中點處被采樣。

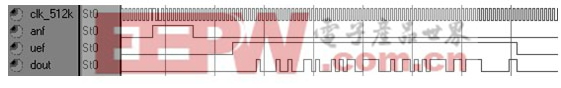

串行數據發送與接受的仿真時序圖如圖3所示。

圖3 同步485仿真時序圖

基于RS-485的同步通信時序是用FPGA作為通信收發器來模擬的,但是通信數據最終是與系統的CPU進行數據交換的。在該通信方式的設計中,通信雙方均采用TI公司的TMS320F2812作為處理器,即通信的控制器。FPGA與DSP的數據交換必須滿足一定的時序,才能保證測速定位單元向車載無線電控制單元實時地傳輸位置及速度信號。本系統中,DSP控制器采用C語言進行軟件設計。

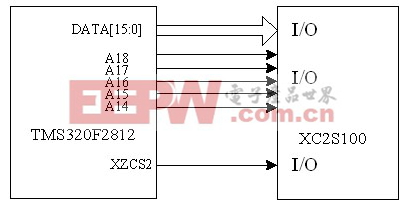

TMS320F2812的外部存儲器XINTF可供選擇的外部地址空間有XINTF0,XINTF2,XINTF6。其中XINTF0 使用XZCS0AND1作為片選信號,外部存儲器擴展空間為8K;XINTF2與XINTF6分別使用XZCS2、XZCS6AND7作為片選信號,外部存儲器擴展空間均為0.5M。測速定位單元在發送位置速度信息時,是通過DSP的數據線傳輸到FPGA,DSP根據相應的外部存儲器片選信號找出對應的地址,在從底層傳感器得到一個新的定位數據后寫入該地址。相對應的硬件連接框圖如圖4所示:

圖4 車輛測速定位單元DSP控制器向FPGA收發器寫數據的硬件連接示意圖

根據協議要求,定位信息每次發送時包括5個字節的用戶數據和2個字節的CRC校驗,因此16bits數據線至少需要連續發送四次才能將底層的定位信息完整地傳送到FPGA。

為了減少硬連線,這里只連接地址線的高五位,對其中的低四位地址線進行4-16譯碼,最高位地址線作為該譯碼器的使能信號。取對應于一個外部存儲器片選信號的四個地址,比如片選信號XZCS2為低(對應的外部存儲器地址范圍:0x080000―0x100000),即可選用0xe0000,0xe4000,0xe8000,0xec000四個地址作為DSP向FPGA寫數據的地址。

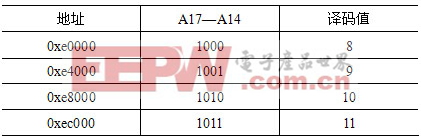

由于每個不同的地址都對應一個地址譯碼值,當四個譯碼值都出現后才可認為一次定位信息傳送完成。這時把連續接收到的七個字節加上幀頭及幀尾作為測速定位單元發送給車載無線電控制單元的一幀數據。相對應的地址譯碼值如表2所示。

表2 地址譯碼值

(2) 車載無線電控制單元側DSP與FPGA的數據交換

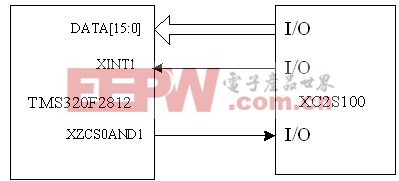

由于采樣時間為毫秒級,為了避免占用過多的CPU資源,車載無線電控制單元中DSP從FPGA讀數據時不采用查詢方式,而采用外部中斷來接收數據。將DSP的16bits數據線與FPGA連接,DSP的XINT1也連接到FPGA的I/O管腳。若選用XZCS0AND1作為外部存儲器片選信號,則DSP從FPGA讀數據的尋址空間范圍為0x002000―0x004000,這個地址范圍內所讀出的數據即為數據線上傳送到DSP的定位數據。相對應的硬件連接框圖如下:

圖5 車載無線電傳輸單元DSP控制器從FPGA收發器讀數據的硬件連接示意圖

評論