基于FPGA的高速大容量FLASH存儲

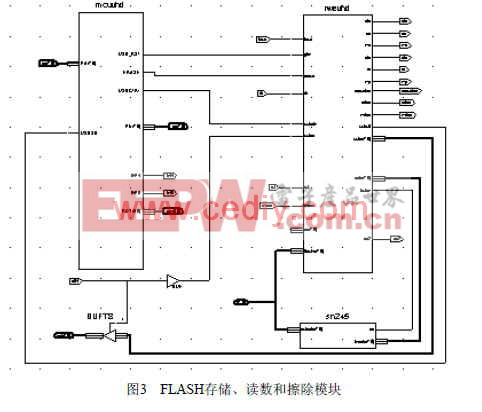

(2) FLASH存儲、讀數(shù)和擦除模塊(如圖 3) FLASH在寫數(shù)據(jù)、讀數(shù)據(jù)和擦除時(shí) [4],編寫控制FLASH的程序,要按照如下規(guī)則:

頁編程:器件的編程以頁為單位,但在一個(gè)頁編程周期中允許對部分頁(一個(gè)或連續(xù)的多個(gè)字節(jié))編程。一個(gè)頁編程周期由串行數(shù)據(jù)加載階段和緊隨的編程階段組成。在數(shù)據(jù)加載階段,數(shù)據(jù)被加載到數(shù)據(jù)寄存器中 ;在編程階段,已加載的數(shù)據(jù)寫入實(shí)際的存儲單元,編程典型時(shí)間為200µs。

頁讀:器件在上電時(shí),就被初始化為讀模式,此時(shí)可以不寫 00h命令,直接寫入地址和30h命令即可。有兩種類型的讀,分別是隨機(jī)讀和順序頁讀。由于設(shè)計(jì)存儲時(shí)

是基于整個(gè)頁操作,所以讀命令使用順序頁讀。命令打入后經(jīng)過最多20µs的時(shí)間,數(shù)據(jù)則會從選擇的頁傳到數(shù)據(jù)寄存器中。

塊擦除:器件的擦除操作是以塊為單位的。塊地址加載由擦除建立命令 60h啟動,然后輸入確認(rèn)命令D0h,執(zhí)行內(nèi)部擦除過程。這一先建立再執(zhí)行的兩步命令時(shí)序,確保了存儲內(nèi)容不會由外部的干擾而意外擦除,擦除時(shí)間典型值為1.5ms。本文引用地址:http://www.104case.com/article/152391.htm

3、系統(tǒng)調(diào)試

電路通過模擬接受一組實(shí)時(shí)串行數(shù)據(jù),經(jīng)過 FPGA串行數(shù)據(jù)轉(zhuǎn)換為并行數(shù)據(jù),并且存儲到 FLASH;再與主機(jī)通信讀回存儲在 FLASH中的數(shù)據(jù) [5]。它已經(jīng)可以穩(wěn)定的工作在 180Mbytes/s的存儲速度,滿足了所需的機(jī)載實(shí)驗(yàn)要求。 USB芯片工作在從方式 (Slave FIFO模式),由FPGA控制芯片的讀寫,同步傳輸數(shù)據(jù)。實(shí)測中通過 USB回放數(shù)據(jù)的速度為 15Mbytes/s。 4、結(jié)論

本文設(shè)計(jì)了基于 FPGA和FLASH存儲測試系統(tǒng),使 FPGA與FLASH各自的優(yōu)點(diǎn)得到了有效的發(fā)揮:本文作者創(chuàng)新點(diǎn): RS-422電平傳輸串行數(shù)據(jù),通過 FPGA把串行數(shù)據(jù)轉(zhuǎn)化為并行數(shù)據(jù)存儲到高速大容量的 FLASH的存儲系統(tǒng)的具體設(shè)計(jì)和實(shí)施,在保證系統(tǒng)工作性能的情況下簡化了系統(tǒng)設(shè)計(jì),并驗(yàn)證了系統(tǒng)設(shè)計(jì)方案的正確性和可行性,為進(jìn)一步工程化實(shí)現(xiàn)打下了良好的基礎(chǔ),具有一定的工程應(yīng)用價(jià)值。

評論