一種靈活的包含嵌入式存儲器的FPGA結構

1.引言

傳統上 FPGA只能實現相對較小的邏輯電路,隨著工藝技術的提高, FPGA的容量和性能也不斷提高,如今 FPGA已經被用于實現大的邏輯電路甚至整個系統。這些大的系統相對于傳統上一直作為 FPGA市場目標的小邏輯分支電路有著很大的不同。其中一個最重要的不同就是這些大的系統中包含存儲器。所以,要有效的在 FPGA中實現存儲器,結構的支持至關重要。包含大的存儲器陣列的 FPGA芯片已經有生產商推出,例如 Xilinx和 Altera。

然而,多數學術性的 FPGA CAD工具只針對于同質的 FPGA,即只包含邏輯模塊和布線資源的 FPGA。本文中我們提出了一種靈活的包含嵌入式存儲器的 FPGA的結構以及一種建立RRG(布線資源圖)的方法。在 FPGA的研究中,我們通常用實驗的方法來評估新結構特性的實用性。因此,我們需要靈活的 CAD工具來對多種結構進行比較。 VPR即是這種類型的 FPGA CAD工具,它適用于多種 FPGA結構。我們開發了一種新的布局布線工具, VA。它增強了 VPR的功能,使得 VPR可以有效地處理包含嵌入式存儲器的 FPGA結構,而且保證了其靈活性。

2.結構

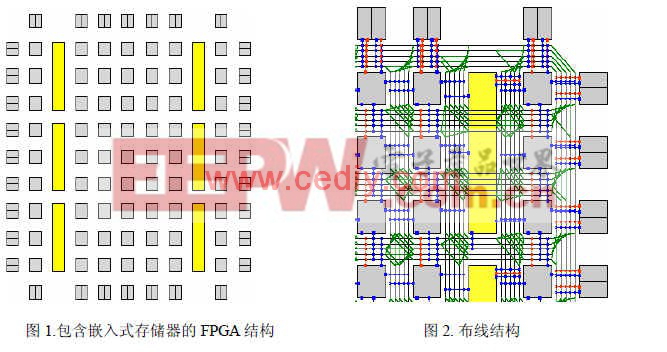

包含嵌入式存儲器的 FPGA結構如圖 1所示。整個 FPGA由四種基本資源構成,邏輯模塊,I/O模塊,布局布線模塊和存儲器模塊。每個存儲器模塊的存儲容量是固定的,但是用戶可以對存儲器模塊進行配置,以實現不同長寬比的存儲器。我們假設存儲器模塊在整個 FPGA芯片中按列排放,如同 Xilinx公司的 Spartan-3系列 FPGA。存儲器模塊的列數,每列存儲器所處的位置、每列存儲器模塊包含的存儲器模塊數目以及每列存儲器模塊中第一個存儲器模塊的起始物理位置都會在結構描述文件中定義,我們將在 3.1中詳細討論。

圖 2所示為我們的 FPGA布線結構,這是一種島式結構。邏輯模塊周圍圍繞了布線通道。每個邏輯模塊的輸入或輸出引腳可以通過一個由可配置開關組成的連接模塊與靠近它的通道中的 8條連線相連。在每一個垂直通道和水平通道交叉處有一個開關模塊。開關模塊給每條輸入信號線提供了三個可能的連接選擇。同邏輯模塊相同,存儲器模塊也通過連接模塊與邏輯布線相連。在文獻 [4]中, S. J. E Wilton等人把模塊的靈活性定義為 Fm,即每個存儲器引腳可以連接的連線的數目。在圖 2中的結構中, Fm=3。Fm的最小值是 1,最大值為 V,這里的 V值即每個布線通道中的連線數目。從存儲器模塊和邏輯模塊之間的連接結構可以清楚的看到,每個存儲器模塊的引腳可以安排在模塊四周,同鄰近的布線通道連接。

3.具體實現方式

存儲器模塊相對于邏輯模塊,有一些不同之處,例如模塊引腳的分布方式、模塊高度等,這使得 RRG的設計非常復雜。在這一部分中,我們將討論一種簡單而且靈活的 RRG設計方法。我們的 RRG設計方法基于 VPR,但是我們作了一些改進使其能夠處理包含嵌入式存儲器的 FPGA的布線問題。

評論