采用統一功率格式的SoC的低功耗設計方案

為了幫助日益壯大的設計隊伍,EDA行業必須為設計人員提供能夠使整個流程順利執行的自動化解決方案。這些解決方案必須對功率進行優化,同時滿足所有其它的設計和市場要求,包括速度、成本和IC制造良率。

本文引用地址:http://www.104case.com/article/151561.htm功率問題概況

通過在系統級進行權衡取舍,作出相關決策,可以最大限度地降低消費設備的功率和能耗。有關系統劃分 (亦即確定哪一種功能性由硬件還是軟件來實現)、元件及IP選擇的決策,對降低功率和系統性能及功能性的影響最大。

例如。在一個基于硬盤的MP3播放器中,對功率管理而言,關鍵的架構性特征之一是軟件控制數據緩沖系統,其允許硬盤每次提供相當于長度幾分鐘的 音樂,然后停止旋轉,等待下一次的音樂。盡管現在許多移動電話都已在架構級對語音通信進行了高度優化,來自消費者的壓力仍然迫使設計師增加從電郵到流視 頻,乃至MP3播放器的大量其它功能。

這樣一來,系統設計師又不得不使用越來越激進的架構來管理功率。為了支持這種工作,EDA行業不斷提高自身的系統級功率建模工具,以向系統設計人員提供關于其架構性決策的影響的反饋信息。

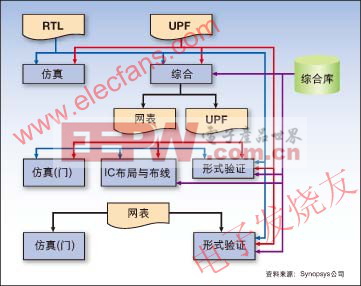

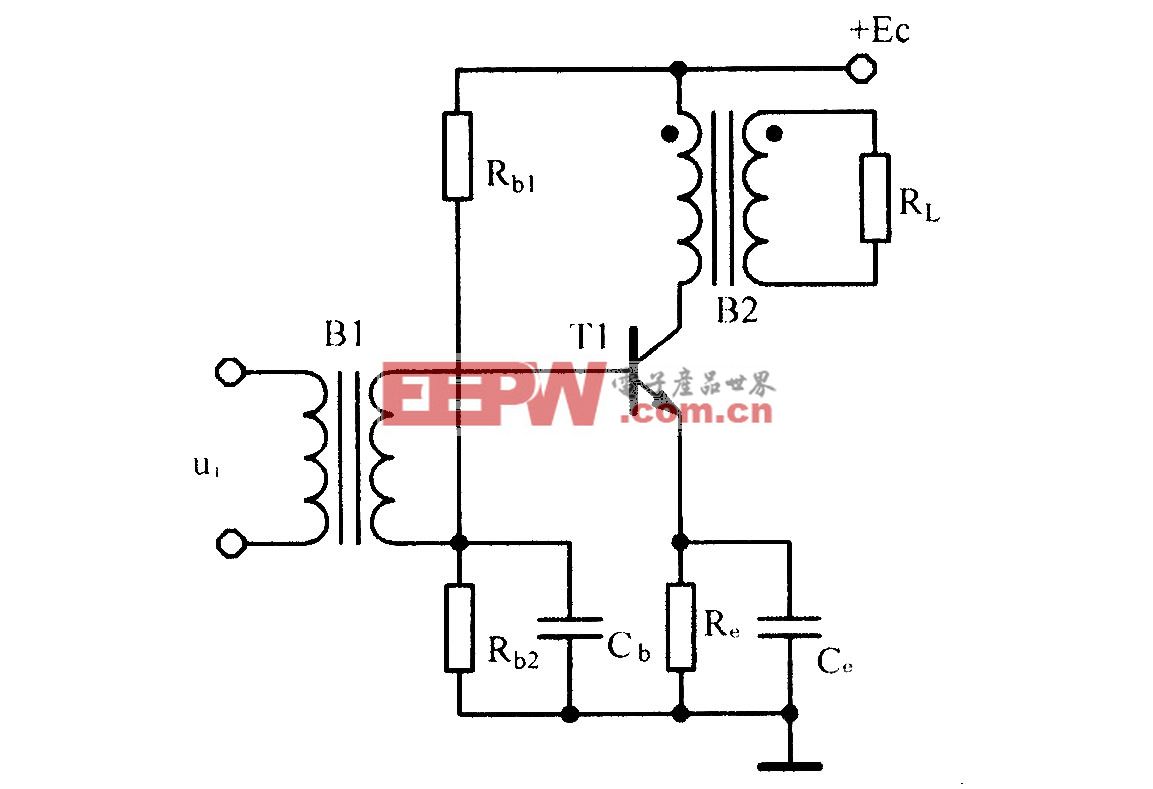

圖:在設計中與golden RTL協作,通過DVFS和功率門控技術,在全設計流程中系統化地使用UPF來降低動態和靜態功耗。

硬件功率管理技術

一旦確定了系統架構,選定了主要的應用IC,就可以運用各種硬件功率管理技術了。

RTL設計人員可以利用各種技術,如時鐘門控、邏輯和單元電路級功率優化,以及多線程電壓設計等,作為一個標準的基于綜合的設計流程的一部分。 這些技術的自動應用可以降低功耗,同時保持性能、可測試性與可制造性。但這需要一個集成時鐘門控單元和邏輯單元的庫來提供多個驅動力度和多個閾值電平,還 需要工具來使用這些單元庫的功能。現在的EDA工具就具有這類能力,而這些技術的使用也越來越普及。而更加激進的功率管理方法仍在設計原則和EDA工具能 力的前沿。

動態功率與V2成正比,故要把動態功率降至最小,關鍵在于降低電源電壓。設計人員已開始采用片上多電壓域:較高的電壓域用于高性能模塊,比如處 理器和緩存;較低的電壓域用于其它工作頻率較低的模塊。該方案需要在工作電壓不同的模塊間插入電平轉換器。這種大膽的設計是根據主要元件(比如處理器)的 工作負載,動態地為它們分配電源電壓和時鐘頻率,被稱為動態電壓頻率調變(DVFS)技術。

隨著工藝幾何尺寸不斷縮小到90納米、65納米及以下,漏電流問題越來越突出,限制了手持設備的電池壽命。為了把泄漏功率降至最低,設計人員開 始采用功率門控技術—關斷未在使用的模塊的電源,通常是利用片上開關關斷。這樣,在那些斷電和上電的域間就需要隔離單元,還需要一種策略來保 存關斷期間的狀態。

對于那些有峰值處理要求(如視頻編碼/解碼)但又有大量時間處于空閑狀態下的消費應用而言,這些技術極為有效。利用一種自適應功率管理方案,設計人員就可以最大限度地提高所設計芯片的性能,而當設計中某些模塊的工作負載減少時使其以超低功率模式工作。

通過正確的硬件設計及其它因素,DVFS和功率門控技術可通過軟件來控制,實現大幅度節能,延長電池壽命。

這些自適應技術都需要更加智能的設計自動化技術和更加靈活的IP。設計人員需要一種辦法來詳細說明功率意圖,即明確哪一個域由哪一個電源供電, 哪一個域可被關斷,以及什么時候采用什么策略來保存關斷期間的狀態。設計人員一般都希望這種設計意圖的確定與RTL無關,因為特定的RTL模塊在不同的應 用中可能有不同的功率意圖。

因此,實現工具需要設置功率意圖,并在適當的位置插入電平轉換器、隔離單元和保持寄存器,并把功率正確路由到芯片中的所有器件。尤其是,這些工具需要對信號進行適當緩沖,亦即,當需要信號時緩沖器上電,不需要時關斷。這些路由規則中有一部分可能會變得相當復雜。

簽核工具現在必須包含電壓依賴性時序和功率網格完整性。驗證(規則的和動態的)必須能夠處理因增加功率門控技術而產生的設計行為的變化。IP供 應商也必須協助開發出范圍更廣泛的低功率IP,包括電平轉換器、隔離單元、保持觸發器和功率門控開關。為了支持DVFS,還必須對單元庫進行特性化以用于 大電壓范圍,而不僅僅局限在一兩個特殊的工作點上。

幸運的是,業界主流公司已開始聯手協作推出低功率解決方案,把更加自動化的EDA工具、更靈活的IP、標準 格式和功耗要求更嚴格的工藝技術整合到真正的端到端解決方案中。最近,Accellera標準組織內有一大批領先的半導體、EDA和IP公司聯盟正在積極 開發一種統一功率格式(UPF)。UPF提供了一個機制來描述與RTL無關設計的功率意圖。它允許設計人員定義功率門控所需的功率域、隔離策略和保持策 略。它還允許設計人員定義電平轉換器策略和功率狀態表,用來處理多個功率域。利用UPF,可以使全設計流程中的所有工具統一化,以實現和驗證同一套功率降 低策略。

在設計中與golden RTL協作,通過DVFS和功率門控技術,在全設計流程中系統化地使用UPF來降低動態和靜態功率。

評論