狀態機“毛刺”的產生及消除方法

if lock1=‘1’ and lock1’event then

regl=d;

end if;

end process;

q=regl;

……

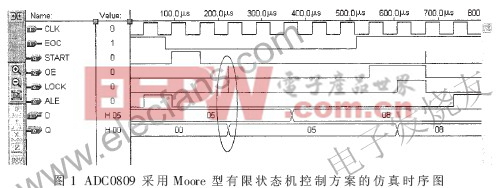

其時序仿真波形如圖1所示。

Moore型狀態機組成框圖如圖2所示。

因為Moore型狀態機的輸出信號來自組合邏輯——輸出譯碼器,輸出信號中帶有“毛刺”,且引起了輸出信號Q的誤動作,結果從其仿真時序圖中可以發現。

在同步電路中,一般情況下“毛刺”不會產生重大影響。因為“毛刺”僅發生在時鐘有效邊沿之后的一小段時間內,只要在下一個時鐘有效邊沿到來之前“毛刺”消失即可。但當狀態機的輸出信號作為其他功能模塊的控制信號,例如作為異步控制、三態使能控制或時鐘信號使用時,將會使受控模塊發生誤動作,造成系統工作混亂。因此,在這種情況下必須通過改變設計消除毛刺。

消除狀態機輸出信號的“毛刺”一般可采用三種方案:

(1)調整狀態編碼,使相鄰狀態間只有1位信號改變,從而消除競爭冒險的發生條件,避免了毛刺的產生。常采用的編碼方式為格雷碼。它適用于順序遷移的狀態機。

(2)在有限狀態機的基礎上采用時鐘同步信號,即把時鐘信號引入組合進程。狀態機每一個輸出信號都經過附加的輸出寄存器,并由時鐘信號同步,因而保證了輸出信號沒有毛刺,如圖3所示。這種方法存在一些弊端:由于增加了輸出寄存器,硬件開銷增大,這對于一些寄存器資源較少的目標芯片是不利的;從狀態機的狀態位到達輸出需要經過兩級組合邏輯,這就限制了系統時鐘的最高工作頻率;由于時鐘信號將輸出加載到附加的寄存器上,所以在輸出端得到信號值的時間要比狀態的變化延時一個時鐘周期。

(3)直接把狀態機的狀態碼作為輸出信號,即采用狀態碼直接輸出型狀態機,使狀態和輸出信號一致,使得輸出譯碼電路被優化掉了,因此不會出現競爭冒險。這種方案,占用芯片資源少,信號與狀態變化同步,因此速度快,是一種較優方案。但在設計過程中對狀態編碼時可能增加狀態向量,出現多余狀態。雖然可用CASE語句中WHENOTHERS來安排多余狀態,但有時難以有效控制多余狀態,運行時可能會出現難以預料的情況。因此它適用于狀態機輸出信號較少的場合。

若對ADC0809的采樣控制采用狀態碼直接輸出型狀態機方案,其主要程序如下:

begin

lock=lock1;

process(current_state,eoc)

begin

case current_state IS

when st0 => next_state =st1;

when st1 => next_state =st2;

when st2 => next_state =st3;

when st3 => if (eoc =‘1’)then next_state =st3; else next_state =st4;end if;

評論