基于FPGA與SRAM的大容量數據存儲的設計

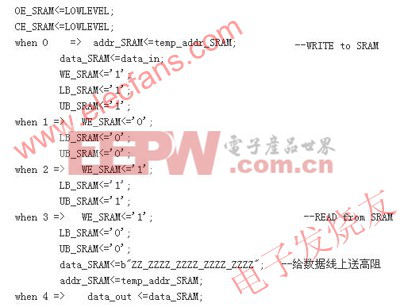

以下是一段用VHDL語言描述的控制RAM的讀寫操作時序的程序代碼:

程序中,在進行讀寫操作時,片選使能信號CE_SRAM及輸出使能信號OE_SRAM始終為低電平。

第0時刻到第2時刻在進行寫操作:第0時刻地址線addr_SRAM和數據線data_SRAM同時賦新值,控制線WE_SRAM、LB_SRAM、UB_SRAM要經歷一個窄脈沖的變化過程,RAM在獲取到此控制線下降沿信息后,便知開始進行寫操作。需要注意的是,雖然數據在第0時刻已賦到數據線上,但因為寫操作是控制線低電平有效,所以數據線上真正發生數據更新是在控制線變為低電平之后,因此,數據線上的實際更新時刻是在第2個時刻。

第3、4狀態是進行讀操作:在讀寫轉換時刻,也就是在第3時刻如前所述需給數據線上送高阻態。這樣,讀取數據的時序關系由系統時鐘進行控制,在第3時刻給地址線上送要讀取的地址,第4時刻將數據端口上的數據送出。這里需注意的是,讀取數據要比讀取地址晚一個時刻。從而,完成了對外部RAM的讀寫操作控制。

4結論

該系統已應用在羅蘭—C導航接收機的信號處理中。實驗證明,此設計可靠穩定地完成了大容量高速異步數據存儲,進一步提高了系統的性能。

評論