基于FPGA與SRAM的大容量數(shù)據(jù)存儲的設計

3.2 引腳功能

(1)A0~A17:18位的地址輸入線;

(2)IO0~IO15:16位的三態(tài)數(shù)據(jù)輸入輸出線;

(3)寫控制線;

(4)片選信號;

(5)輸出使能信號;

(6)低字節(jié)、高字節(jié)使能信號;

(3)~(6)的控制線均為低電平有效。

3.3 控制邏輯電路設計

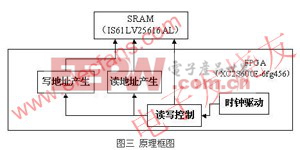

如圖三所示,控制邏輯由FPGA來實現(xiàn)。主要包括讀地址產生器、寫地址產生器、讀寫時鐘信號產生器及讀寫控制等幾部分。下面分別加以講述。

(1)寫地址產生器:由于設計時采用256K×16的SRAM,故有18位地址,寫地址產生器用18位計數(shù)器實現(xiàn)。靠外部時鐘驅動,每進行一次寫操作后,讀寫控制單元產生計數(shù)脈沖,使其增1,直到18位計數(shù)器計滿再循環(huán)寫入地址為0的空間。

(2)讀地址產生器同上,也采用18位計數(shù)器實現(xiàn),根據(jù)系統(tǒng)要求,每隔一定的采樣周期將讀地址指針偏移一定偏移量,并從該位置讀取數(shù)據(jù)。

(3)讀寫地址選擇器由于讀寫地址復用管腳,因此在讀寫操作時,必須選通相應的地址。這就需要由FPGA控制芯片上的等控制信號來對SRAM進行讀寫的操作。

(4)此外,由于讀寫之間的切換,數(shù)據(jù)線上的數(shù)據(jù)在切換瞬間如不加處理會出現(xiàn)混亂現(xiàn)象。因此,為避免讀、寫操作發(fā)生沖突,數(shù)據(jù)線呈三種狀態(tài),讀數(shù)據(jù)、寫數(shù)據(jù)及高阻態(tài)。在從寫到讀的過程中需給數(shù)據(jù)線上送高阻態(tài)。

(5)當需要對SRAM進行寫操作時,由FPGA控制產生寫地址選通信號,該選通信號為一單脈沖形式,如圖四中該脈沖下降沿觸發(fā)SRAM,告知開始對RAM進行寫操作,使FPGA輸出寫地址,同時給數(shù)據(jù)線上送數(shù)據(jù)。在寫操作期間,片選信號始終保持低電平,而寫地址選通信號上升沿到來時使寫地址計數(shù)器增1。以此類推,通過寫地址選通信號高低電平變化完成對數(shù)據(jù)依次寫入。需要注意的是,地址線和數(shù)據(jù)線在為高時可同時賦新值,但只有在變低后賦予數(shù)據(jù)線上的新值才有效。

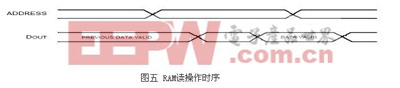

對SRAM進行讀操作相對較簡單,在進行讀操作期間,始終為低電平,始終為高電平。每進行一次讀操作,地址按系統(tǒng)要求變化一次。同時注意,地址的變化時刻總要先于數(shù)據(jù)的變化時刻。圖五為RAM讀操作時序。

評論