基于FPGA與SRAM的大容量數據存儲的設計

1 前言

本文引用地址:http://www.104case.com/article/151496.htm針對FPGA中內部BlockRAM有限的缺點,提出了將FPGA與外部SRAM相結合來改進設計的方法,并給出了部分VHDL程序。

2 硬件設計

這里將主要討論以Xilinx公司的FPGA(XC2S600E-6fg456)和ISSI公司的SRAM(IS61LV25616AL)為主要器件來完成大容量數據存儲的設計思路。

FPGA即現場可編程門陣列,其結構與傳統的門陣列相似,大量的可編程邏輯塊( CLB , Configurable Logic Block ) 在芯片中央按矩陣排列,芯片四周為可編程輸入/輸出塊( IOB , Input / Output Block),CLB行列之間及CLB和IOB之間具有可編程的互連資源(ICR,InterConnectResource)。CLB、IOB和ICR都由分布在芯片中的SRAM靜態存儲單元控制,SRAM中的數據決定FPGA的功能,這些數據可以在系統加電時自動或由命令控制從外部存儲器裝入。

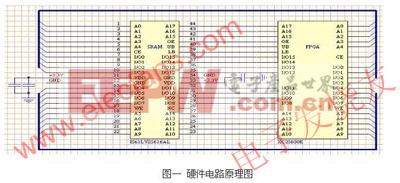

在進行數據存儲時,可直接將數據寫入FPGA內部的BlockRAM中,在一定程度上減少了FPGA的資源分配。但FPGA內部自帶的RAM塊畢竟是有限的,當需進行大容量數據存儲時這有限的RAM塊是遠遠不能滿足系統設計要求的。此時,就需要將FPGA與外部RAM相結合完成大容量數據存儲。具體硬件電路如圖一所示:

3 IS61LV25616AL功能簡介

IS61LV25616AL是IntegratedSiliconSolution公司(ISSI)的一款容量為256K×16的且引腳功能完全兼容的4Mb的異步SRAM,可為Xilinx公司的Spartan-2E系列FPGA提供高性能、高消費比的外圍存儲。除了256K×16異步SRAM外,ISSI還提供128K×16、512K×16、256K×8、512K×8和1M×8的異步SRAM。 IS61LV25616AL引腳結構框圖如圖二所示:

3.1 主要特征

(1)工作電壓:3.3伏;

(2)訪問時間:10ns、12ns;

(3)芯片容量:256K×16;

(4)封裝形式:44引腳TSOPII封裝,也有48引腳mBGA和44引腳SOJ封裝;

(5)采用0.18μm技術制造。

評論