基于DDS的電路板檢測儀信號源設計

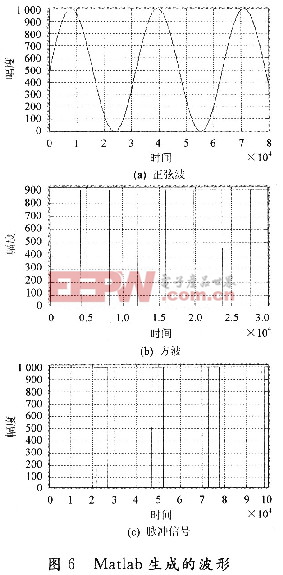

圖5和圖6顯示了頻率控制字為68h產生的正弦波、頻率控制字為346h的方波和頻率控制字為27Fh的脈沖信號的功能仿真波形。從功能仿真波形可以看出,DDS電路能夠很好地產生電路板檢測儀所需激勵信號。

3.2 硬件驗證

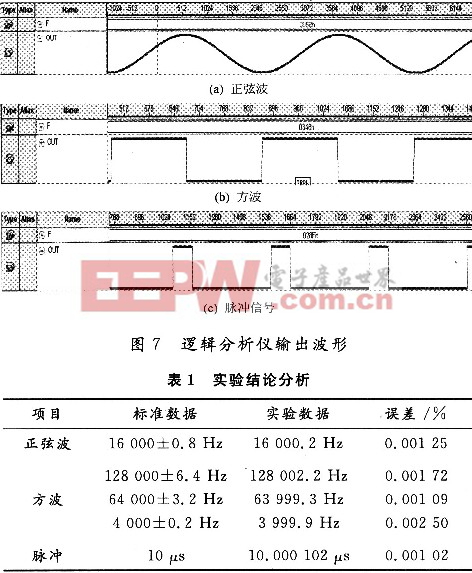

為了能夠更清晰地分析DDS電路,采用DE2-70開發板結合SignalTapⅡ型嵌入式邏輯分析儀對設計進行實時的硬件驗證。首先對DDS頂層電路圖做部分修改,主要是進行管腳設定。將修改后的頂層文件下載到DE2-70中,通過SignalTapⅡ型嵌入式邏輯分析儀實時觀測FPGA輸出波形,如圖7所示。SignalTapⅡ所能顯示的被測信號的時間長度為T,計算公式如下:

![]()

式中:N為SignalTapⅡ的緩存中存儲的采樣點數,Ts為SignalTapⅡ采樣時鐘的周期。由圖7和式(3)可得出表1所示結論。

產生誤差的主要原因有兩方面,一是截斷誤差,ROM查找表的地址輸入是相位累加器的高11位;二是正弦波量化引入的誤差,將正弦信號量化為二進制數必然引起誤差。

4 結語

通過對DDS電路的功能仿真和硬件驗證,可以看出DDS可以有效地產生所需波形信號。較傳統的信號發生器,可以減小體積、降低功耗、提高可靠性和靈活性并縮短了開發周期,具有較高的實用價值。

評論