基于ADSP-TS201S的多DSP并行系統設計

5 系統軟件設計

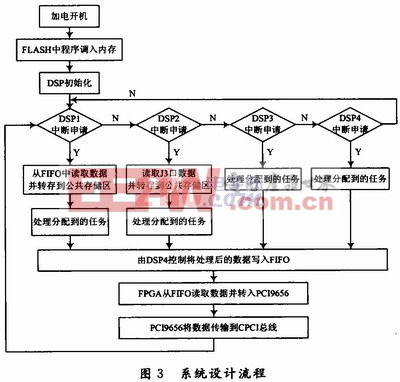

由于系統硬件是基于DSP+FPGA的結構,相應的軟件也分為兩個功能模塊。FPGA主要完成整個系統的數據傳輸邏輯控制,因此FPGA具體的處理流程嵌套在DSP的信號處理流程中。4片DSP主要完成信號的處理,大致的系統設計流程如圖3所示。本文引用地址:http://www.104case.com/article/151299.htm

4片DSP并行工作時,總線仲裁策略指定DSPl為主處理器,由它完成系統的初始化、數據程序配置、與CPCI工控機主機通信等,并參與運算工作。當系統 接收到數據時,首先判斷信號的傳輸方式,若是并行信號,由FPGA進行相應處理后寫入FIFO中,同時通過外部中斷告知DPS-l,隨即DSPl發出中斷 申請,總線仲裁令DSP1獲得總線控制權,讀取FIFO中的數據并轉存至公共存儲區;然后DSP1通過LINK口與其他DSP通信,進行任務分配,其他 DSP依次循環獲得總線控制權,讀取數據進行處理然后再存入存儲區;最后,由DSP4控制將存儲區里的數據寫入FIF-O,同時通知FPGA讀取并完成時 序轉換后傳輸到PCI9656,由PCI9656將數據傳輸到CPCI總線,完成這一幀數據的處理。若系統接收到的數據是由J3口傳輸來的串行信號,則先 由DSP2發出中斷申請,總線仲裁令DSP2獲得總線控制權,將接收到的數據轉存至公共存儲區;然后通過同樣的方式在4片DSP間進行任務分配和處理,由 DSP4寫入FIFO,最后由FPGA和PCI9656聯合將數據傳輸到CPCI總線,完成串行信號的處理。

6 結語

本文介紹了一種基于PFGA的多DSP并行處理系統的設計,重點對DSP并行結構設計進行了分析,并介紹了FPGA設計和外部設備接口設計。實際應用表 明,該多DSP并行處理系統應用于寬帶雷達信號處理時,能夠滿足任務中的各項指標,還能完成設計外的其他功能,并且易于控制,穩定可靠。本文提供的系統設 計方案能夠為處理寬帶雷達信號的其他研究人員提供一定的參考。

評論