基于ADSP-TS201S的多DSP并行系統設計

摘要:為滿足寬帶雷達信號處理對處理速度和實時性的要求,提出一種基于4片ADSP-TS201S的DSP并行系統設計。通過分析比較3種ADSP-TS2 01S的并行處理結構,結合實際需求,采用外部總線共享與鏈路口混合耦合的多DSP并行處理系統方案。在設計中,利用FPGA實現數據傳輸和CPCI接口的邏輯控制。經驗證,該系統具有運算能力強、片間通信靈活、并行處理效率高等優點。

關鍵詞:多DSP并行系統;ADSP-TS201S;FPGA;CPCI接口

0 引言

在寬帶雷達信號處理中,存在諸如回波采樣率高、脈沖壓縮(匹配濾波)運算量大、處理流程復雜、實時高分辨目標檢測困難等一系列問題。針對這些問題,采用通 用計算機平臺難以應對運算量大和實時性等高要求,因此,需采用專用的數字信號處理器(DSP)來進行高速運算。盡管當前的數字信號處理器已達到較高水平, 但單片DSP芯片的處理能力還是不能滿足寬帶雷達的性能要求,需要引入并行處理技術,在本設計中使用4片DSP芯片組成并行處理系統。另外,為充分發揮 DSP芯片在復雜算法處理上的優勢及FPGA在大數據量的底層算法上的優勢,設計了一種基于FPGA控制的多DSP并行處理系統。

1 系統設計

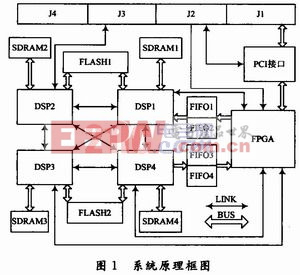

基于FPGA控制的多DSP并行處理系統的原理圖如圖1所示。

整個雷達信號處理系統以高可靠性CPCI工控機為平臺,內置不同功能的信號處理板。板間的數據傳輸通過CPCI接口完成。根據雷達信號處理系統的任務分 配,本系統負責完成中頻數字信號的處理。根據前端信號采集板輸出數據的不同,數據將以串行或并行的方式輸送到本系統中。其中,串行信號通過CPCI的J3 口以差分的形式直接傳輸給DSP2,然后在4片DSP芯片間按照預定的算法進行任務分配和并行處理,處理完畢后通過DSP4寫入兩片擴展連接成32輸出方 式的FIFO中,此時,FPGA直接從FIFO中讀取數據,完成與CPCI接口芯片PCI9656的時序轉換后將數據發送到PCI9656,通過CPCI 總線經J1和J2口傳輸到雷達系統的其他功能模塊。對于并行信號而言,32位帶寬的信號首先通過J3口發送到F-PGA內部寄存器中FPGA接收到數據后 將數據寫入輸入緩存區,并在完成一幀后給并行DSP輸出中斷。當并行DSP采樣到中斷后,從數據緩存區讀取數據,完成處理后,將數據傳輸到緩存 區,FPGA再通過相同的處理方式經CPCI接口的J1口和J2口將數據傳輸到雷達系統的其他功能模塊。

評論