針對FPGA的完全可配置嵌入式32位RISC處理器

使用嵌入式微處理器的FPGA設計不斷增長。根據Dataquest的統計,一年大約啟動10萬個FPGA設計項目,其中約30%包含某種形式的微處理器。

本文引用地址:http://www.104case.com/article/151169.htm形成這種趨勢有幾個方面的原因。首先,數據流應用更適合可編程硬件,同時嵌入式微處理器更適合于執行控制流的應用。第二,要改變設計時,嵌入式處理器呈現更大的靈活性。最后,用軟核的嵌入式微處理器消除了處理器過時的風險。從傳統上而言,對嵌入式FPGA微處理器有一些限制,包括成本,速度和設計性能。隨著工藝技術和設計技術的進步,這些限制正在不斷改善,現在設計人員更有可能在他們的應用中考慮使用嵌入式FPGA微處理器。

與過去相比,現成的微處理器已經大大比嵌入式微處理器便宜。但是,今天的低成本FPGA被證明是一個節約成本的解決方案。如果設計中已經使用了FPGA,處理器可以整合到現有的FPGA架構,節省了分立器件或新的FPGA成本。設計周期也是一個重要的因素。將硬件與微處理器子系統構成相關的架構并進行實施能有多快?編寫,測試和在微處理器上調試運行的代碼需要多久?在過去幾年中,在整體功能和易用性方面,針對嵌入式微處理器開發的軟件工具也有了明顯的改善。因此,現在可以在幾分鐘內運行設計,并且進行測試。產品上市的時間縮短了,因為現在用軟件實現功能比硬件更快,更簡單。

用現成的微處理器達到的性能有良好的歷史記錄。隨著技術的改進,FPGA在功能和整個系統的速度方面有了顯著的進步。由于現在的FPGA能夠處理更大的帶寬,嵌入式處理器對于許多設計有很大的吸引力。此外,由于FPGA與其他專用模塊的緊密配合,軟IP核的擴展性提供了一個系統接口,就性能和吞吐量方面而言,現在一個片上處理器可以提供卓越的設計方案。

當評估諸如LatticeMico32這樣的特殊處理器時,使用嵌入式軟處理器的優點非常清楚。

一個典型的嵌入式處理器子系統

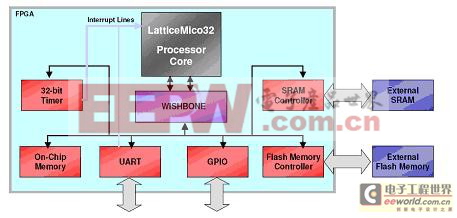

讓我們來看看一個典型的嵌入式處理器子系統,例如,LatticeMico32軟處理器。該處理器需要有能與外界通信的功能,因此通常核連接到一個片上總線系統,在此情況下是WISHBONE開放源代碼總線。然后還需要一個存儲系統,用來保存處理器程序代碼以及處理器核使用的數據。對外部通信而言,在一個典型的系統中有各種接口,從簡單的通信接口和連接、更復雜的協議到應用中的專用硬件模塊。現在該處理器總線架構需要連接外設和存儲器系統。一個典型的系統如圖1所示。

圖1 典型的嵌入式RISC處理器子系統

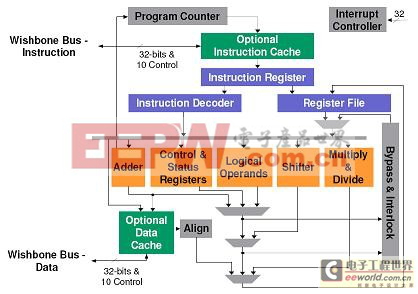

讓我們來看看處理器核本身:LatticeMico32是基于哈佛總線結構的RISC架構的微處理器(圖2)。 RISC體系結構提供了一個簡單的指令集和更快的性能。哈佛總線架構提供獨立的指令和數據總線,能夠執行單周期指令。該處理器擁有32個通用寄存器,可處理多達32個外部的中斷。定制的處理器可以插入乘法器或桶形移位器,以及不同的調試功能。

圖2 LatticeMico32:一個可配置的RISC處理器核

linux操作系統文章專題:linux操作系統詳解(linux不再難懂)

評論