基于FPGA的語音端點檢測

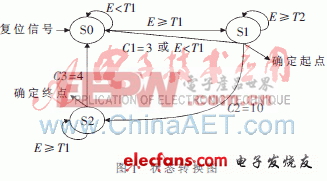

具體判斷過程為:(1)在S0狀態下,E

2 實驗結果

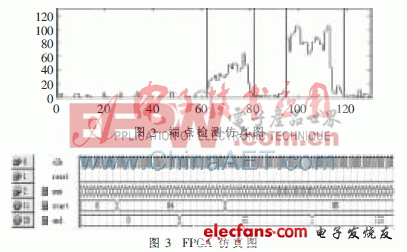

實驗時的聲音樣本采用電腦聲卡采集(16 kHz,8 bit)的“wav“文件, 并對常用的詞語進行實驗。圖2是詞“長沙”在Matlab上的端點檢測仿真結果圖,其中橫坐標代表幀號、縱坐標代表幀能量。兩個字的語音段分別是64~82幀和95~120幀。圖3是詞“長沙”在QuartusⅡ上仿真的結果圖,其中num代表每幀的幀號,start代表語音開始的幀號,end代表語音結束的幀號。從圖1、圖2可以看出詞“長沙”的端點檢查仿真結果在Quartus Ⅱ上的和Matlab上是一致的,從圖中可以看出改進后的端點檢測方法檢測效果非常好。

本文在加窗的過程中合理地運用了DSP Builder工具,簡化了硬件的設計,同時也加快了處理速度,是一種很值得借鑒的FPGA加窗方法。在端點判斷的算法上,用改進的Lawrence Rabiner端點檢測法,對算法門限的計算和起止點判斷做了改進,并用有限狀態機實現了FPGA的設計,實驗證明該算法在低信噪比的情況下能準確地找到語音信號的起止點。與其他一些端點檢測方法相比,該算法更加簡單、穩定,所需的存儲空間小,是一種理想的硬件端點檢查方法,對語音識別系統的開發和設計有一定的參考價值。

評論