H.264算法的DSP移植與優(yōu)化

2.3 ICT/反ICT和量化

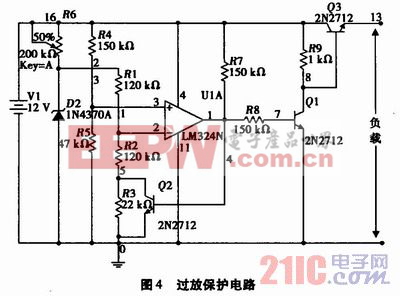

原始的ICT/IICT和量化算法不能夠充分發(fā)揮DSP的并行優(yōu)勢,以至于8個功能單元在編碼的過程中都處于閑置狀態(tài),存儲器中的數(shù)據(jù)被頻繁重復的訪問也導致了DSP運行效率的降低。在圖4所示中,提出對于ICT/IICT和量化部分的算法圖例,一個宏塊中所有基于4×4塊的IC-T/IICT變換都能夠同時執(zhí)行,這充分利用了DSP的8個功能單元。實驗結(jié)果表明,經(jīng)量化后,計算一個ICT/HCT的4×4塊僅僅需要12個平均周期。這一優(yōu)化不但提高了算法的速度又顯著地降低了碼流大小,使視頻信號的實時處理成為可能。本文引用地址:http://www.104case.com/article/150854.htm

3 實驗結(jié)果分析

在600 MHz的TMS320DM643平臺上,通過開發(fā)軟件CCS載入開源代碼X264構(gòu)架對CIF格式的5個視頻序列(Akiyo,News,F(xiàn)oreman,F(xiàn)ootba-ll,Mobile)進行了相關實驗。在這5個視頻序列中,Akiyo和News序列有較低的運動級別,背景變化畫面人物運動幅度不大,而Foreman和Fo-otball有高的運動級別,運動劇烈有場景切換,最后一種Mobile序列則有復雜的背景。表1列出了在量化步長(QP)為25的情況下,原始H.264編碼器和優(yōu)化后的H.264編碼器之間的對比結(jié)果。從中可以看出,原始的編碼器的編碼速度是2~3 f/s,而優(yōu)化后的編碼速度是前者的10倍多。

4 總結(jié)

本系統(tǒng)采用TMS320DM643作為的核心處理器,這款DSP芯片主要是為實現(xiàn)低功耗、高性能而專門設計的定點DSP芯片。它具有高度靈活的可操作性和高速的處理能力,先進的多總線結(jié)構(gòu),主要應用在通信、數(shù)據(jù)采集等系統(tǒng)中,特別在實時性方面效果最佳。

本設計借助開源代碼X264在CCS開發(fā)平臺進行試驗,測試了編碼優(yōu)化前后的幀率等各種性能,旨在尋求更高效的視屏編碼算法。

評論