USB2.0主機控制器IP核的設計

摘要 :為了擺脫對USB2.0 主機控制器ASIC 芯片的依賴,提高產品集成度,本文設計了針對全速和高速USB 海量存儲設備的USB2.0 主機控制器IP 核。首先介紹USB2.0 主機控制器IP核中主要涉及的USB2.0 通信協議以及與物理層芯片接口的ULPI 接口規范協議,并依據協議規范,利用VHDL 硬件描述語言完成USB2.0 主機控制器IP 核的ULPI 接口模塊以及USB2.0通信協議模塊的設計。使用Xilinx 公司的ISE Simulator 工具進行波形仿真,并在XilinxXUPV2 開發板上進行驗證,仿真結果及FPGA片上實驗表明本文設計的USB2.0 主機控制器能夠完成對USB 海量存儲設備的有效管理。

本文引用地址:http://www.104case.com/article/149851.htm0 引言

在USB 協議標準發展的過程中,USB2.0 接口憑借其連接簡單、穩定、速度快以及即插即用等優點,廣泛應用于計算機、通信和消費類電子產品中。然而目前大部分USB 主機端控制器都是使用國外公司研制的專用ASIC 芯片,USB2.0 主機控制器IP 核的設計可以擺脫對這些芯片的依賴,使得應用靈活方便。本文完成了針對全速和高速海量存儲設備USB2.0主機控制器IP 核中與物理層芯片接口的ULPI[2]模塊以及USB2.0 協議模塊的設計和實現。

ULPI 模塊介于USB2.0 主機控制器的協議模塊和物理層芯片之間,完成對插入USB 設備的狀態檢測,判別是何種設備(全速還是高速),然后將設備置于相應的狀態再進行USB 的各種傳輸事務。每一個USB 的傳輸都是由事務組成的。而每一個事務都是由USB 傳輸的最基本單位包(packet)來組成的,USB 的包主要是由令牌包、數據包、握手包和特殊包這四種類型組成的。令牌包和數據包又包含不同的類型[4],握手包僅由一個PID 域組成用以傳輸聯絡信號來反映目前數據處理的狀態。USB 協議包含了四種數據傳輸類型,分別為控制傳輸,批量傳輸,中斷傳輸和同步傳輸,其中控制傳輸是所有設備必須要支持的傳輸方式,對時間沒有嚴格限制的大量的數據傳輸要用到批量傳輸;同步傳輸也被稱為實時傳輸。

1 系統設計

圖1 整體系統圖

圖 1 中FPGA型號為Xilinx Virtex-II proxc2vp30,標識為ISP1504 的子板通過FPGA擴展口接入到FPGA 開發板,子板以物理層芯片ISP1504 為核心并配以簡單外圍電路構成,上面帶有USB 接口用來插入USB 設備。ISP1504 用來完成數據的串行化和解串,以及NRZI編碼和比特位填充等功能。FPGA 中內嵌microblaze 軟核處理器,USB 主機控制器IP 核作為用戶IP 核掛接到處理器的PLB 總線上,再加入USB 驅動,便可以實現microblaze 處理器對全速和高速USB 海量存儲設備的管理。本文主要介紹USB 主機控制器IP 核設計中的兩個重要模塊--與物理層接口的ULPI 模塊以及USB2.0 協議層模塊的設計實現。

2 ULPI 接口模塊的設計及實現

ULPI(UTMI+低引腳數)接口規范是應用于高速通用串行總線(USB)和便攜式USB(USBOTG)收發器芯片的行業規范。ULPI 模塊提供USB 主機控制器與UTM 正常通信的物理層通道,是主機控制器實現正常通信的重要接口之一。該模塊依據ULPI規范實現了總線事件檢測的功能,完成了上電,正常操作,掛起和復位狀態之間的轉換等。

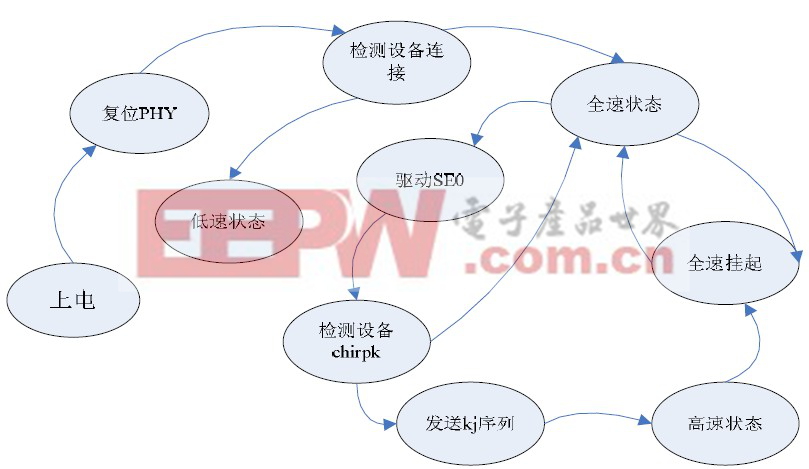

此模塊采用狀態機來實現,主要通過對 ISP1504 的功能控制寄存器寫入一定的數據,使得物理層芯片的收發器進入相應的狀態(全速、高速以及高速掛起),對狀態機中時間控制采用計數器實現,主機端發送kj 序列對首先通過寫ISP1504 的功能控制寄存器使之進入高速chirp 檢測狀態,然后在數據線上發送全0 和全1 來完成的。本設計USB2.0 主機控制主要針對全速和高速海量存儲設備設備,全速和高速的狀態轉移圖如圖2 所示:

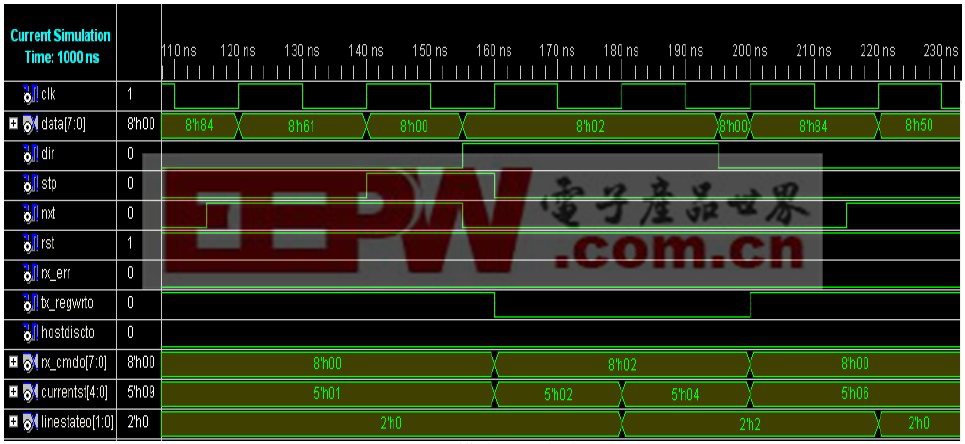

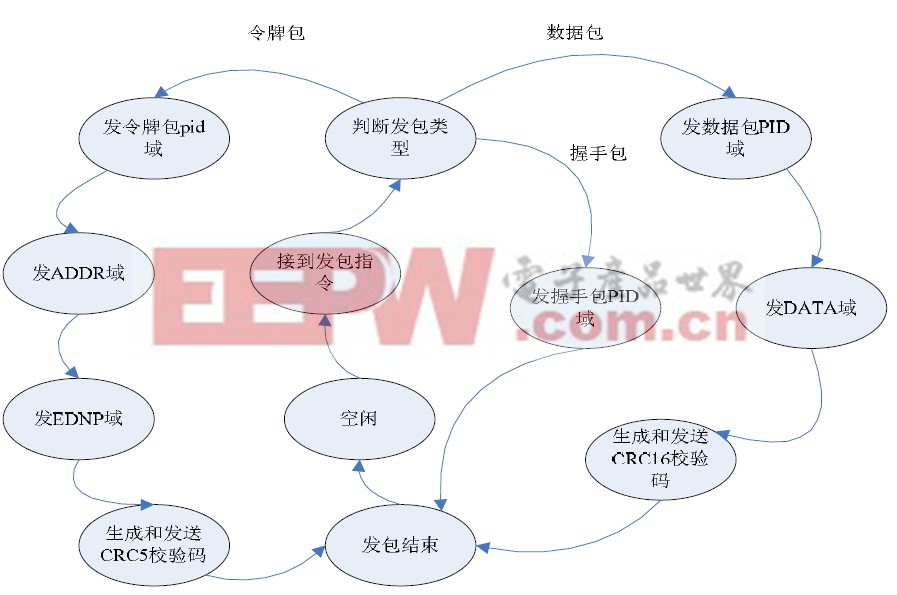

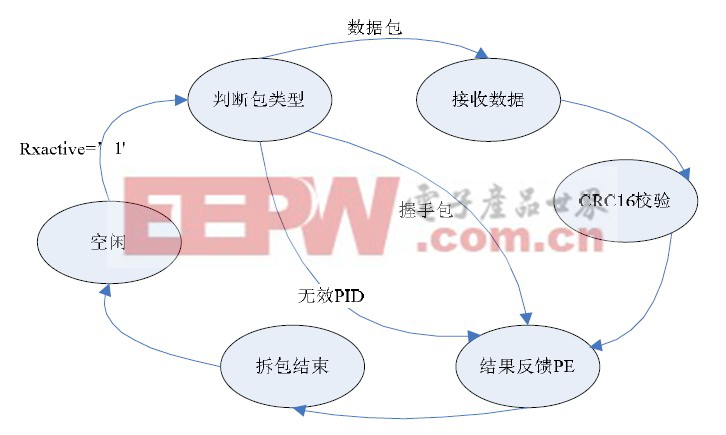

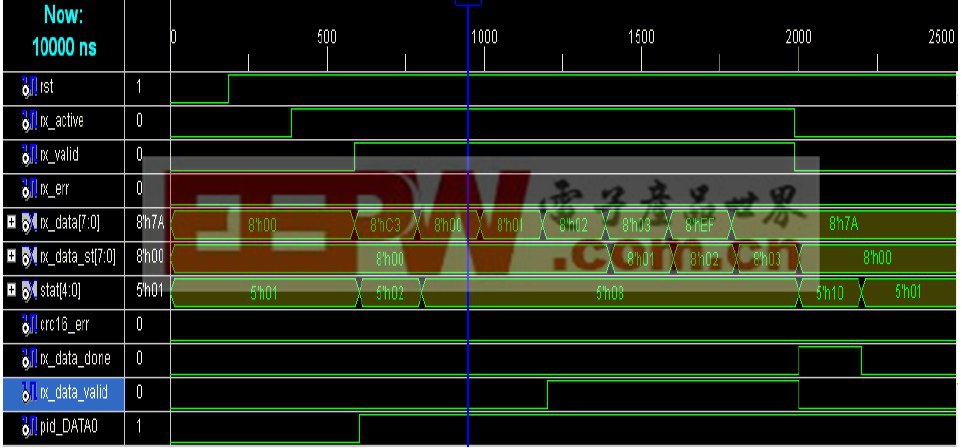

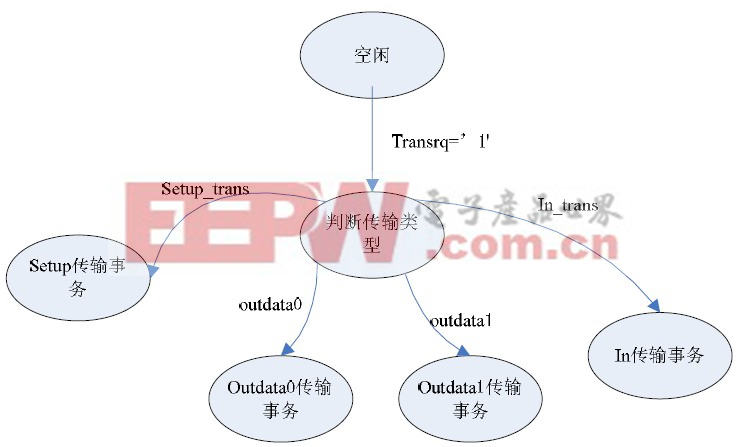

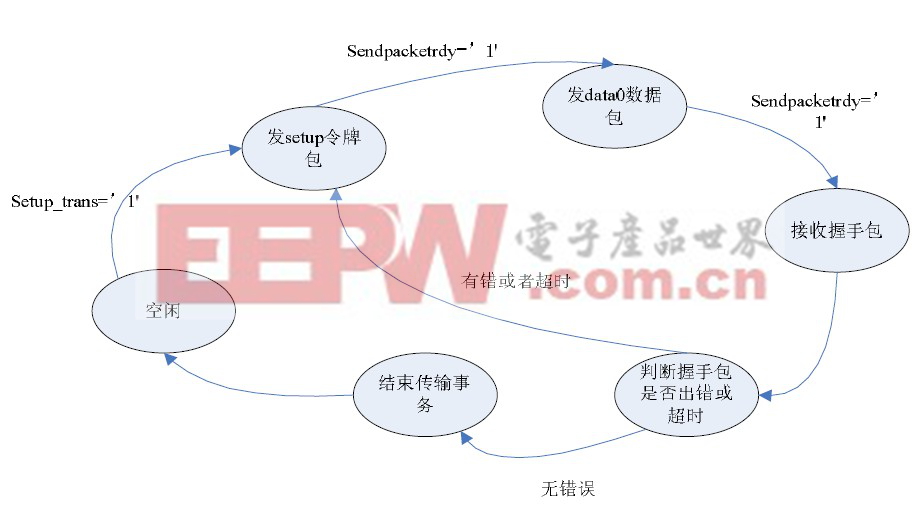

圖 2 ULPI 模塊狀態轉移圖 芯片上電之后,通過寫ISP1504 的功能控制寄存器的reset 位來復位芯片,之后通過差分數據線的狀態來檢測是否有設備插入,并根據狀態判斷是低速設備還是全速設備(D-為高電平,即連接的設備為低速設備。若D+為高電平,即連接的設備為全速設備。)需特別說明的是,主機端對高速設備的檢測并不是一下完成的,是首先置為全速設備,然后主機端通過設置控制功能寄存器驅動出SE0 信號,如果收到設備發回的chirp k信號,主機端就會發送線性調頻的kj 序列對,每個k 或者j 持續時間在40-60us,如果設備是高速設備,在檢測到主機發過來的3 個kj 序列對之后設備的控制器會使其自身進入高速模式,即高速收發正常的操作狀態。如果沒有收到設備返回的chirp k 信號則認為是全速設備回到全速狀態下進行傳輸。當總線上沒有數據傳輸(空閑狀態)超過3ms,則會進入FS 掛起狀態,當收到主機端發送的resume信號時恢復到FS狀態,同理如果在高速狀態下空閑超過3ms,會先進入FS掛起狀態。 用 VHDL 硬件描述語言完全按照上述狀態機轉移完成此模塊,在Xilinx ISE 開發環境下使用ISE simulator 仿真工具進行仿真,仿真波形如圖3 所示: 圖3 ULPI模塊的仿真波形 由于狀態轉移對時間的限制,故只截取了部分狀態作分析。由圖所示,currentST[4:0]反映的是狀態機的狀態,linestate[1:0]表示線上狀態(直接反映D+ D-狀態),在狀態1 通過向ISP1504 的84H 地址(控制功能寄存器的地址)寫入61H(置位rst 位)復位物理層芯片。 在狀態1 寫完寄存器后置位stp,轉到狀態2 檢測設備連接狀態。在狀態2,當檢測到linestate變為10(D+為高),所以先識別為全速設備,轉到全速狀態4。在下一個時鐘周期進入狀態6 驅動se0 對設備進行復位,然后按照狀態轉移圖最后進入高速操作階段。 3 USB2.0 協議模塊的設計和實現 在 ULPI模塊完成了設備的狀態監測和轉移之后,等進入正常的全速或者是高速模式,就可以按照USB2.0 協議完成數據的傳輸,USB2.0 協議實現模塊是主機控制器實現的核心模塊,完成USB 數據的讀寫和傳輸方式的控制。根據協議層的功能主要把協議層分成三個子模塊來實現,分別是封包模塊(PA)、拆包模塊(PD)以及控制傳輸的協議引擎模塊( PE )。 3.1 PA PD 模塊的設計實現 封包模塊(PA)需要對令牌包、數據包和握手包三種包按照其對應格式分別進行封裝并發送到ULPI 模塊。開始空閑狀態,接到發包指令后,判斷發包類型然后進入相應的狀態。例如令牌包需將其PID 域、ADDR 域、ENDP 域以及CRC5 校驗域按照順序封裝完成后發送。 狀態轉移圖如下所示: 圖4 PA模塊狀態轉移圖 拆包模塊(PD)剛好是封包模塊的逆過程,該模塊是把從ULPI 模塊接收到的數據包和握手包進行拆包。對數據包拆包首先就是要判斷PID 域以確定數據包的類型,并且還需對數據進行CRC 校驗然后根據該數據包的功能將數據域內容送給要保存數據的模塊,圖5 是拆包模塊的狀態轉移圖: 圖 5 PD 模塊狀態轉移圖 仿真結果如圖6 所示: 圖 6 拆包的仿真波形 在圖6 中,完成一個包含三個數據域的拆包過程。信號rx_valid 和rx_active 同時有效時rx_data[7:0]代表從ULPI 模塊接收到的數據,首先根據接收PID 域值為C3,判斷出該數據包的類型為DATA0,pid_data0 信號為高。Rx_data_st 保存拆包完成后的數據域,數據是在rx_data_valid 信號為高電平期間存入rx_data_st 寄存器的,所以接收數據為0x00、0x01、0x02、0x03。最后對接收的CRC 部分進行了驗證,由于0xef、0x7a 是此包數據域正確的CRC 生成碼,所以傳輸無誤情況下crc16_err 一直為0。 3.2 PE 模塊的設計實現 協議引擎(PE)模塊主要負責協調PA 和PD 模塊實現USB 傳輸方式,本設計主要實現兩種傳輸方式即控制傳輸方式和批量傳輸方式。該模塊設計的主狀態轉移圖如圖7 所示,狀態機在空閑狀態收到請求傳輸有效信號transreq后,就會對請求類型transtype進行判斷。不同的transtype 值代表著不同的傳輸事務要求。按照不同的要求,主狀態機就會轉到相應的傳輸事務狀態中進行處理。 圖 7 PE 模塊主狀態轉移圖 每個傳輸事務由不同的狀態轉移過程來實現,以其中的setup 傳輸事務為例。首先,狀態機向PA 模塊發送發包使能標志,同時將表示setup 令牌包的值1101送給PA 模塊。PA模塊接到發setup 包指令,就會按照要求完成封包發送的工作,最后反饋給PE 模塊一個發包結束的信號sendpacketen。setup狀態機接收到發包結束信號sendpacketen為'1'后,就會轉到下一個狀態發data0 數據包。在此狀態下如果收到發包結束有效信號,也會轉到下一狀態接收握手包。在這個狀態中,主要是和PD 模塊進行通信。PD 模塊通過對接收的握手包進行拆包,來分析包的PID 域是否出錯。如果沒有錯就會反饋給PE 模塊包的類型,出錯就通過信號來通知PE 模塊。狀態機本狀態除了要判斷接收包是否出錯,還要判斷接收包是否超時。各個事務分別完成之后,至此協議層完成。 圖 8 Setup 事務狀態轉移圖 4 結論 本文完成了 USB2.0 主機控制器中ULPI 模塊與USB2.0 協議層模塊設計,此USB2.0 主機控制器 IP 核主要針對全速和高速海量存儲設備。設計采用VHDL 語言進行RTL 級描述,使用Xilinx 公司的ISE simulator 工具進行波形仿真,仿真結果驗證了設計的正確性,并且在Xilinx XUPV2 FPGA 開發板[8]和帶有USB接口并以物理層芯片ISP1504為核心的子板上進行了驗證。本文設計的USB2.0 主機控制器可作為獨立的IP 核移植到其他數字系統中,擺脫對USB2.0 主機控制器ASIC 的依賴,提高產品集成度。

pid控制器相關文章:pid控制器原理

評論