基于IP復用和SOC技術的微處理器FSPLCSOC模塊設計

1 引言

本文引用地址:http://www.104case.com/article/149525.htm文中采用IP核復用方法和SOC技術基于AVR 8位微處理器AT90S1200IP Core設計專用PLC微處理器FSPLCSOC模塊。

隨著芯片集成程度的飛速提高,IC產業中形成了以片上系統SOC(System-on-Chip)技術為主的設計方式。一個電子系統或分系統可以完全集成在一個芯片上,同時IC設計能力和EDA工具卻相對落后于半導體工藝技術的發展,兩者之間日益加劇的差距已經成為SOC技術發展過程中一個突出的障礙。采用基于IP復用技術進行設計是減小這一差距惟一有效的途徑,IP復用技術包括兩個方面的內容:IP核生成和IP核復用。

2 IP核復用

IP核復用(IP Core Reuse)是指在集成電路設計過程中,通過繼承、共享或購買所需的知識產權內核(第三方IP核),然后再利用EDA工具進行設計、綜合和驗證。IP核是IP復用的載體和核心內容,基于應用需求、規范協議和行業標準的不同,IP核的內容也是千差萬別的。在IC產業中,IP核被定義為用于ASIC, ASSP, PLD等芯片中,且預先定義好功能、經過驗證的、可重復利用的電路功能模塊,如PCI接口核、ADC核,FIR濾波器核、SDRAM控制器核等。根據IC設計層次的不同。IP核分為以下三類:軟IP(Soft IP)、硬IP(Hard IP),固IP (Firm IP)。文中主要涉及到軟IP核設計和復用。軟IP是可類比、綜合的硬件描述語言(HDL)模型,通常是可綜合的RTL模型,包括邏輯描述、網表和測試的文檔(Testbench)。軟IP設計周期短、投人少,與工藝無關,可靈活修改,在設計中只須對時序、面積和功耗進行修正,可復用性最高。基于軟核的設計(Soft Core-based design)是一種非常實用的SOC設計方法。它將系統的功能劃分為不同的軟核,包括微處理器、ALU、ROM、PC、ROM、I/0等。由于軟IP核僅提供能夠綜合的HDL描述,因此復用前需要深人地了解HDL文件描述的RTL模型,采用適當工藝技術的標準單元庫,再重新進行綜合、布局布線、后仿真提取網表、驗證時序等反復工作,最后集成到SOC設計中,因此SOC設計即生成的IP核和第三方復用IP核集成整合。

3 FSPLC微處理器IP核設計

3.1 IP軟核生成

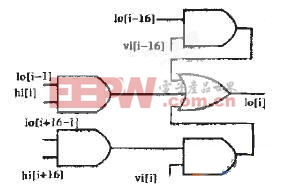

文中基于AVR8位微處理器分析實際PLC梯形圖及其指令表,設計邏輯處理器LP、布爾處理器BP、存儲器位接口MBI等3個模塊用于提高PLC執行速度,下面以邏輯處理器LP單元模塊為例,描述IP軟核生成。PLC梯形圖包括8種基本電路:左分支觸點LBC/非觸點LBCN,右分支觸點RBC/非觸點RBCN, 雙分支觸點DBC/非觸點DBCN,不分支觸點NBC/不分支非觸點NBCN。文中根據這8種基本電路設計一個16xl6觸點矩陣電路,即邏輯處理器LP單元,矩陣中各個觸點由電子電路模擬PLC梯形圖基本電路。在任何一個觸點上包括橫線輸入、豎線輸入、引出輸出線圈。觸點矩陣中共有256個橫線輸入圈節點hi,240個豎線輸入圈節點vi,256個輸出線圈Io。當一行超過16時,轉向下一行,以此構成矩陣電路,如hi[i],vi[i],lo[i]表示某個觸點的橫線輸入、豎線輸入、輸出,那么其同行的下一個觸點的橫線輸入、豎線輸入、輸出分別為hi[i+ 1]、vi[i+1]、lo[i+1],其同列的下一個觸點hi[i+16]、vi[i+16]、lo[i+16],那么輸出觸點的表達式為

I0[i]=I0[i-1]hi[i]+vi[i-16]lo[i-16]+vi[i]lo[i+16-1]hi[ i+16] 。

以此各個觸點彼此互相連接組成處理梯形圖的觸點矩陣。如圖1所示。

圖1 LP單元觸點電子電路模擬

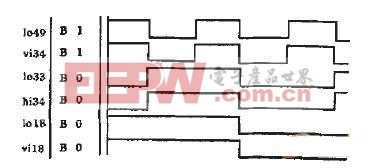

邏輯處理器LP采用Verilog描述,借助Model-Sim進行功能仿真,驗證模塊功能的正確性。LP單元功能仿真波形如圖2所示。

圖2 LP單元功能仿真波形

驗證功能正確后,借助Synosys的綜合工具Synplify Pro對模塊進行綜合。綜合包括Compiling、Mapping、Optimization。綜合時將經ModelSim。功能仿真驗證的源代碼調人Synplify Pro,執行Compiler,編譯后,創建約束文件。sdc,編輯約束文件對模塊添加約束條件,包括時鐘、面積、扇人扇出、延時等,添加約束后執行綜合,產生網表文件。EDF。根據綜合后給出的。log文件觀察Constraint文件中的約束條件是否滿足需要,例如按照給出的“Worst Path Information,修改約束以滿足Worst Path的要求。綜合完成后在Quartus Ⅱ4。0展開網表文件,布局布線后編譯形成。sof文件,將此文件下級到Alters Nios開發板進行驗證,驗證正確后再借助ModelSim進行時序驗證。

3.2 AVRIP核復用

AVR8位微處理器AT90S1200IP核由opencores。org提供。整個微處理器IP核包括ALU、PC、SRAM、IR、ROM、I/0,控制等”個模塊,可以分成3個單元;取指單元、執行單元和I/0單元。指令執行時,取指單元負責取出下一個指令,執行單元負責執行當前指令,而LO單元負資和外界的連接。取指單元和執行單元組成微處理器的CPU。

整個AVRIP核包括許多寄存器:指令寄存器、指令備份寄存器、程序計數器、通用寄存器、存儲地址寄存器(MAR),1/O口控制寄存器等。整個系統的工作就是基于這些寄存器之間的數據傳輸。設計所有的寄存器以及它們之間的組合邏輯及其連接就是系統的數據通道設計。控制模塊決定怎樣進行寄存器傳愉。數據通道和控制單元組成了整個微處理器。

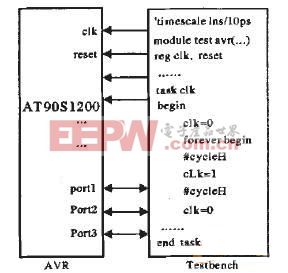

對于AT90S12001P核復用,考慮到IP核在SOC中集成整合,首先須徹底了解所復用核的架構和指令集,借助ModelSim進行功能仿真,建立Testbench平臺測試波形驗證功能的正確性,如圖3所示。編譯無誤且功能正確后借助Synplify Pro對IP核飾代碼進行邏輯綜合,如果VHDL程序正確無誤并且其編程風格符合Synplify Pro綜合要求,Synplify Pro將產生一個網表文件(。EDF文件),再借助QuartusA4。0和ModelSim分別進行FPGA驗證和時序驗證,此過程不斷循環,直至復用的微處理器IP核沒有任何錯誤。

圖3 AVRIP復用測試平臺Testbench框圖

p2p機相關文章:p2p原理

評論