基于ADSP-TS201S的二維DMA數據傳輸

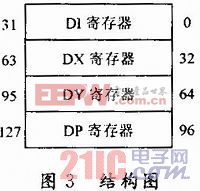

DMA傳輸控制塊寄存器是一個128位的四字組寄存器,含有DMA塊傳輸所需的控制信息。在DMA發送時,4個字包含了原數據的地址、將要發送的字數量、地址增量和控制位。在DMA接收時,4個字包含了目的地址、將要接收的字數據數量、地址增量和控制位,其結構如圖3所示。本文引用地址:http://www.104case.com/article/149491.htm

其中,DI寄存器是一個32位的DMA索引寄存器,它包括了將要發送或者接收的數據源地址或者目的地址,既可以指向內部寄存器和外部寄存器,也可以指向鏈路口。DX寄存器包含一個16位的汁數值和一個16位的修改量,計數值保存在高16位,修改量保存在低16位。如果使能了二維DMA,則該寄存器保存的只是X方向的計數值和修改量。計數值和修改量均以32位字為單位。DY寄存器和DX寄存器結合使用,該寄存器保存了Y方向上的16位修改量和16位計數值。如果只是進行一維的DMA傳輸,就不需要設置該寄存器。DP寄存器包含了DMA傳輸的所有控制信息。22位到31位包含了所有控制信息,0位到21位包含了鏈式信息。

一般情況下啟動二維DMA的步驟如下:

(1)保存TCB DI寄存器中的當前地址,啟動一個DMA存儲器周期。

(2)在該周期內,將TCB DX增量寄存器中的X修改量與TCB DI寄存器中的當前地址相加。

(3)TCB DX計數寄存器內容減1,若TCB DX計數寄存器值為零,則執行第4步。

(4)重新加載TCB DX計數寄存器值。

(5)DMA寄存器中Y維增量加到TCB DI寄存器中的當前地址。

(6)TCB DX計數寄存器內容減1。

(7)若TCB DX計數寄存器值等于零,則DMA傳輸結束,在再次設置TCB前,需禁止它。

2 二維DMA應用

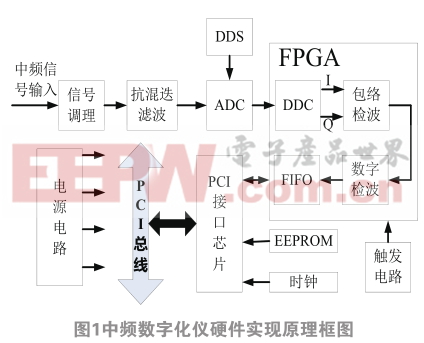

2.1 硬件設計

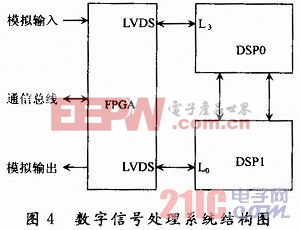

水聲信號處理系統的復雜性和連續性要求信號處理系統具有較高的實時處理能力,所以設計時采用多片TS201來構成并行處理系統,以提高系統的數據處理能力。各DSP之間僅通過鏈路口無縫連接,片間連線少,降低了PCB布線難度和層數,節約了制板成本。此外,數據傳輸采用鏈路口的二維DMA方式,并不占用DSP內核的運算時間,可以提高處理板的實時性能,保證系統流水線操作的順利執行。系統硬件結構圖見圖4所示。

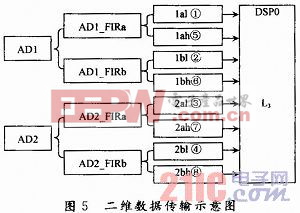

模擬輸入端采用2片18位的高速A/D進行模數轉換,每一片A/D的數據分別經過FPGA中的4個FIR濾波器,產生的8路并行數據通過鏈路口二維DMA傳送給DSP組,進行相應的數字信號處理。具體數據傳輸框圖見圖5所示。

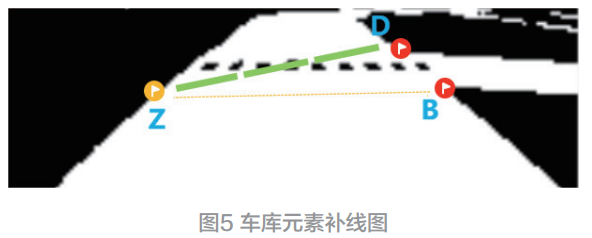

其中,①,②,…,⑧表示LVDS鏈路口數據傳輸順序;lal表示AD1數據經過FIRa濾波器后的低1 KB數據,lah表示AD1數據經過FIRa濾波器后的高1 KB數據。濾波后的A/D數據進入乒乓緩存,最后通過鏈路口將數據傳輸到DSP內部。這里要求,在下一個數據塊采樣結束之前,需要完成上一個數據塊的傳輸、濾波、相關及功率譜分析等一系列較為復雜的數據處理。由于AD1,AD2是同步采樣的,經過數字濾波器的數據通過LVDS鏈路口順序傳輸,為了減少數據塊調整和挑選的時間,這里采用鏈路口的二維DMA傳輸方式,可以快捷地將A/D采集的數據塊按照流水順序寫入DSP內部存儲區。

2.2 軟件設計

以圖4中所示的FPGA與DSP0的L3鏈路口的二維DMA數據傳輸為例,假設數據塊大小設定為1 024點,其鏈路口數據排列順序如圖6所示。

上標表示DSP0內部存儲區內的偏移地址,每次DMA中斷傳輸4×1 024個數據,即每次傳輸4行1 024列大小的數據,8次DMA中斷即可獲得一個時間片內的2個A/D采集數據經過4個FIR濾波器后的全部數據,而且數據塊按照DSP0的流水線順序排列。

評論