SoC系統中AHB/VCI Wrapper的設計及驗證

BVCI請求握手控制單元按照BVCI請求握手協議接受來自BVCI主動方的請求內容信息,并把它們插入請求內容FIFO(速率不匹配情況)或直接傳送到AHB控制一側(速率匹配情況)。

BVCI響應握手控制單元從響應內容FIFO中取出BVCI響應內容信息,并按照BVCI響應握手協議把它們驅動到BVCI主動方。

請求內容FIFO是一個異步FIFO(寫端口與讀端口分別工作在不同的時鐘域),它只有當VCI主動方設備和AHB總線之間速率不匹配時才工作。

響應內容FIFO為一個異步/同步模式可配置的FIFO,當VCI主動方設備和AHB總線之間速率不匹配時,它工作在異步模式(寫端口與讀端口分別工作在不同的時鐘域)否則FIFO工作在同步模式(寫端口與讀端口工作在同一時鐘域),只需完成BVCI響應內容信息的緩存功能即可。

AHB主設備控制引擎在BVCI和AHB之間進行控制信號的轉換。還支持AHB主設備所具備的對總線異常傳送(錯誤、重試傳送)情況的處理能力。

1.3 AHB target Wrapper的設計

AHB-target-Wrapper作為一個AHB從設備,其主要作用是把AHB傳送轉換為符合VCI協議的傳送。

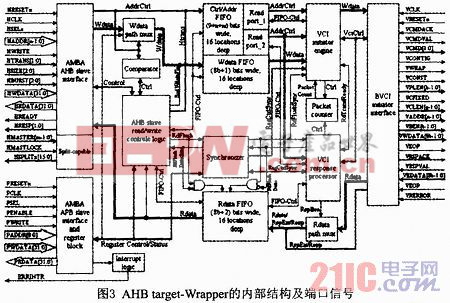

1.4 AHB target Wrapper的總體構架

圖3給出了AHB-target-Wrapper的總體構架,它由各種控制邏輯、數據通路、數據緩沖單元和寄存器組成,主要包含十三部分:寄存器塊、AHB從設備讀寫控制邏輯、地址/控制信息FIFO、寫數據FIFO、讀數據FIFO、VCI主動方引擎、VCI響應處理機、比較器、包計數器、同步裝置、寫數據路徑選擇復用器、讀數據路徑選擇復用器和中斷邏輯。本文引用地址:http://www.104case.com/article/149065.htm

(1)寄存器塊完成對AHB-target-Wrapper的配置和控制以及對其當前工作狀態的反應。

(2)AHB從設備讀寫控制邏輯,具備AHB總線從設備的控制功能。

(3)地址/控制信息FIFO主要用來存放AHB傳送單元的地址/控制信息,以起到緩沖目的。

(4)寫數據FIFO主要用來存放進行寫操作時的數據,以起到寫數據緩沖目的。

(5)讀數據FIFO主要用來存放進行讀預取操作時的數據,以起到讀數據預取目的。它也是一個雙端口的同步/異步可配置FIFO(一個寫端口,一個讀端口),當AHB總線和VCI從動方設備之間速率不匹配時工作在異步模式下,匹配時工作在同步模式下,同步/異步模式的切換可通過配置寄存器來實現。

(6)VCI主動方引擎把符合AHB傳送協議的地址/控制信息轉換為符合BVCI標準的請求內容信息,并按照BVCI請求握手協議把請求內容信息驅動到VC從動方設備。

(7)VCI響應處理機按照BVCI響應握手協議接收由VCI從動方設備返回的響應內容信息,并進行相應的處理。

(8)比較器用于讀預取操作情況,比較正在進行的讀預取操作和AHB上新發來的讀操作是否為同一個讀交易。

(9)包計數器用來統計當前VCI主動方引擎發出的多個BVCI請求包中沒有被響應的請求包個數,其主要目的是為VCI主動方引擎提供有關當前請求包是否正在被響應的信息。

(10)同步裝置在兩個時鐘域的交叉處,即從HCLK到VCLK域和從VCLK到HCLK域的兩個數據流方向上,分別對內部控制信號進行同步。

(11)寫數據路徑選擇復用器根據AHB的傳送單元大小、字節地址和地址大小端模式來選擇AHB寫數據總線上相應的字節通道并把它復制到沒選通的字節通道上。

(12)讀數據路徑選擇復用器根據BVCI響應字節使能(按照一定的算法,由AHB讀交易的傳送單元大小、第一個傳送字節地址以及BVCI的地址模式自動轉換生成)來選擇BVCI讀數據總線上相應的字節通道并把它復制到沒選通的字節通道上。

(13)中斷邏輯當內部電路在執行寫操作過程中發生傳送錯誤時,產生錯誤中斷源,同時根據中斷屏蔽寄存器來決定相應的中斷源是否開放,根據中斷清除寄存器來清除相應的中斷源。

2 AHB/VCI、Wrapper的硬件實現

本文分別給出了AHB-initiator-Wrapper和AHB-target-Wrapper的總體構架,并對兩者內部的各個功能模塊及控制部件的結構設計進行了詳細敘述,同時對兩者的可配置性也進行了充分考慮。在本章最后,對AHB/VCI Wrapper進行了RTL級Verilog硬件建模并進行了初步的門級綜合及電路規模預估。

評論