采用分布式算法的低通FIR濾波器設計

本文引用地址:http://www.104case.com/article/148520.htm

數據接收是在每個時鐘下降沿時檢測轉換完成信號,如果完成,則存入對應的存儲器中,對于N階的系統,就需要存儲N個數據等待處理。然后利用數據選擇器依次選擇各個數據,對數據的每一位進行檢測和提取,組成算法中所需要的數據。在控制信號的作用下利用累加器對數據疊加、移位處理即可實現。

最后,FPGA向DAC0832的數據輸入口(D10~D17)輸送數據。提供DAC0832數據鎖存允許控制信號ILE,高電平有效。提供DAC0832控制信號(CS:片選信號;Xfer:數據傳輸控制信號;WRl、WR2:DAC寄存器寫選通信號),低電平有效。

3 仿真實驗、工況信號測試實驗

基于分布式算法低通FIR濾波器選用xilinx公司的virrex-Ⅱpro器件,在isel0.1下進行設計。利用modelsim 6.5對濾波器進行仿真。系統采用頻率為500 kHz的分頻時鐘,在FPGA中產生一個高頻方波和一個低頻鋸齒波信號,并對兩個信號進行疊加。疊加后的信號作為輸入,對應圖中DIN,經過系統處理后輸出結果對應圖中RESULT,仿真結果如圖3所示。

由圖3中可以看出,本系統存在相位偏移和濾波后依然存在雜波信號的缺點,相位偏移主要是由濾波處理滯后于輸入引起的,比較穩定且偏移較小,一般情況下可以忽略;雜波信號由系統階數較低和系數量化誤差引起的。實際應用中可根據情況選擇適當階數的濾波器和提高采樣頻率予以解決。

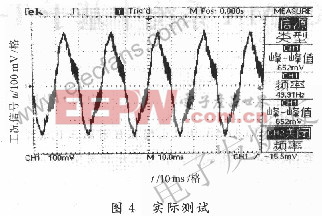

工況信號測試實驗。由信號發生器同時產生一個50 Hz低頻信號和一個5 kHz高頻信號,然后對兩個信號進行疊加,作為被測的工況信號。被測的工況信號經過A/D轉換、濾波處理、D/A轉換,然后在示波器中顯示,如圖4所示。輸出波形中過濾掉了高頻信號部分,同時低頻信號能夠通過該濾波器。由圖4中可以看出,濾波處理后與實際信號還存在一定的誤差。誤差主要是由于算法中采用了低階濾波器、系數量化誤差、器件精度低等原因所致,該誤差可以控制在允許范圍,還可以通過選擇高精度的器件和增加濾波器的階數得以提高。

4 結語

實驗結果表明,基于分布式算法低通FIR濾波器的優點是工作可靠,濾波精度較高,且具有占用資源少,運算速度快。在資源允許的條件下可根據實際應用任意確定濾波器的字長和階數,在高速數字信號處理領域可以得到很好的應用。

評論