多核DSP系統(tǒng)高速傳輸核心的IP設(shè)計(jì)

3.1.1 發(fā)送緩沖IP模塊設(shè)計(jì)

在雙口SRAM的外圍設(shè)計(jì)了較復(fù)雜的控制邏輯構(gòu)成發(fā)送緩沖區(qū),A口和B口的地址計(jì)數(shù)器的地址由兩部分組成:ID號(hào)和地址遞加計(jì)數(shù)邏輯。A口的輸入數(shù)據(jù)來自于RapidIO封裝的數(shù)據(jù)幀,而B口的輸出數(shù)據(jù)又被送到了RapidIO發(fā)送狀態(tài)機(jī)內(nèi),只不過B口的數(shù)據(jù)是需要重發(fā)的數(shù)據(jù)。

因?yàn)?a class="contentlabel" href="http://www.104case.com/news/listbylabel/label/RapidIO">RapidIO數(shù)據(jù)幀最大為68個(gè)雙字,發(fā)送窗口數(shù)被設(shè)計(jì)成7,所以已經(jīng)發(fā)送的數(shù)據(jù)在這個(gè)雙口SRAM中是分段保存的。當(dāng)RapidIO發(fā)送狀態(tài)機(jī)開始發(fā)送數(shù)據(jù),同時(shí)對(duì)數(shù)據(jù)進(jìn)行封裝時(shí),A口的寫信號(hào)有效,并且A口的計(jì)數(shù)器進(jìn)行遞增計(jì)數(shù),遞增計(jì)數(shù)器和段地址構(gòu)成了A口的有效地址。這樣已發(fā)送的數(shù)據(jù)就被保存在這個(gè)以雙口SRAM為核的緩沖區(qū)隊(duì)列中(最多為476個(gè)雙字?jǐn)?shù)據(jù))。在這個(gè)雙口SRAM的外圍設(shè)計(jì)了段指示變量用來指示在該段中保存字?jǐn)?shù)據(jù)的個(gè)數(shù)(因?yàn)榘l(fā)送的數(shù)據(jù)可能有不夠256個(gè)字節(jié),即64個(gè)雙字的情況)。

相鄰節(jié)點(diǎn)返回的數(shù)據(jù)響應(yīng)幀內(nèi),包含相鄰節(jié)點(diǎn)希望接收的下一個(gè)數(shù)據(jù)幀的序號(hào)ID,當(dāng)數(shù)據(jù)響應(yīng)幀類型為datanot accept或data retry類型時(shí),激活了發(fā)送狀態(tài)機(jī)內(nèi)的重發(fā)機(jī)制,B口當(dāng)前地址和A口的段指示變量進(jìn)行比較,當(dāng)B口的當(dāng)前地址和A口相應(yīng)的段指示變量相等時(shí),通知發(fā)送狀態(tài)機(jī)該數(shù)據(jù)已經(jīng)被重新發(fā)送完畢,結(jié)束幀的發(fā)送。只有該幀數(shù)據(jù)的正確的響應(yīng)幀被接收到時(shí),A口才能繼續(xù)發(fā)送新的數(shù)據(jù),并且發(fā)送緩沖區(qū)的窗口向前滑動(dòng)。通過使用這種方法,已發(fā)送的數(shù)據(jù)就源源不斷地保存在這個(gè)緩沖區(qū)隊(duì)列中,而且不會(huì)丟失。

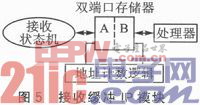

3.1.2 接收緩沖IP模塊設(shè)計(jì)

在雙口SRAM的周圍加入了一些外圍的控制電路構(gòu)成了接收緩沖區(qū)。雙口SRAM的A口和接收狀態(tài)機(jī)相連,雙口SRAM的B口和處理器接口相連。A口和B口分別使用了地址計(jì)數(shù)邏輯。接收緩沖IP模塊如圖5所示。本文引用地址:http://www.104case.com/article/148059.htm

由于RapidIO的一個(gè)數(shù)據(jù)幀是以272字節(jié)封裝的,并且在數(shù)據(jù)幀的第80個(gè)字節(jié)處插入了一個(gè)CRC校驗(yàn)序列,這樣就增加了判斷的難度。當(dāng)接收機(jī)開始接收數(shù)據(jù)幀內(nèi)嵌入的第一個(gè)CRC校驗(yàn)序列時(shí),通過接收狀態(tài)機(jī)進(jìn)行判斷:當(dāng)接收到的第一個(gè)CRC校驗(yàn)序列和接收狀態(tài)機(jī)本地產(chǎn)生的CRC一樣時(shí),A口的地址計(jì)數(shù)電路繼續(xù)計(jì)數(shù);當(dāng)接收到的第一個(gè)CRC校驗(yàn)序列和接收狀態(tài)機(jī)本地產(chǎn)生的CRC不一樣時(shí),說明前面接收到的數(shù)據(jù)是無效的,此時(shí)地址計(jì)數(shù)電路停止計(jì)數(shù),并且地址指示變量減去20。

當(dāng)接收完一個(gè)數(shù)據(jù)幀內(nèi)的所有有效數(shù)據(jù)時(shí)(不包括數(shù)據(jù)幀末尾的CRC校驗(yàn)碼),地址計(jì)數(shù)電路停止計(jì)數(shù),同時(shí)在接收狀態(tài)機(jī)內(nèi)進(jìn)行判斷:當(dāng)接收到的數(shù)據(jù)幀末尾的CRC校驗(yàn)序列和接收狀態(tài)機(jī)本地產(chǎn)生的CRC校驗(yàn)序列一致時(shí),地址指示變量的值不變;當(dāng)接收到的數(shù)據(jù)幀末尾的CRC校驗(yàn)序列和接收狀態(tài)機(jī)本地產(chǎn)生的CRC校驗(yàn)序列不一致時(shí),地址指示變量減63(標(biāo)準(zhǔn)的數(shù)據(jù)幀內(nèi)的有效數(shù)據(jù)是64個(gè)字)。通過這樣的方法在由這個(gè)雙口SRAM構(gòu)造的接收數(shù)據(jù)緩沖區(qū)內(nèi)保存了一個(gè)完整有效的數(shù)據(jù)幀。

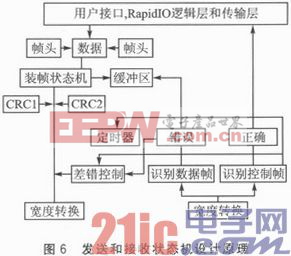

3.2 發(fā)送/接收狀態(tài)機(jī)

發(fā)送狀態(tài)機(jī)和接收狀態(tài)機(jī)模塊包含了RapidIO協(xié)議的差錯(cuò)控制和流量控制的功能。差錯(cuò)控制功能主要是通過使用CRC校驗(yàn)機(jī)制和定時(shí)器機(jī)制來完成的。發(fā)送狀態(tài)機(jī)和接收狀態(tài)機(jī)是通過相互交換內(nèi)部信息來實(shí)現(xiàn)對(duì)數(shù)據(jù)進(jìn)行差錯(cuò)控制和流量控制的,如圖6所示。

3.2.1 發(fā)送狀態(tài)機(jī)模塊設(shè)計(jì)

如圖6所示,來自處理器接口的原始數(shù)據(jù)依次傳送到RapidIO的邏輯層和物理層時(shí),在數(shù)據(jù)的頭部封裝了地址、序號(hào)和長(zhǎng)度等頭部信息,同時(shí)發(fā)送狀態(tài)機(jī)得到每個(gè)數(shù)據(jù)的CRC碼;當(dāng)數(shù)據(jù)大于80個(gè)字節(jié)時(shí),在第80個(gè)字節(jié)的后面插入1個(gè)CRC碼,然后在該數(shù)據(jù)幀的尾部插入1個(gè)CRC碼,這樣就將一個(gè)原始的數(shù)據(jù)轉(zhuǎn)換成了1個(gè)RapidIO數(shù)據(jù)幀,然后將這個(gè)封裝的數(shù)據(jù)幀傳到串行化數(shù)據(jù)模塊進(jìn)行發(fā)送。

如果數(shù)據(jù)幀被對(duì)方節(jié)點(diǎn)正確的接收,則發(fā)送端口可以繼續(xù)發(fā)送數(shù)據(jù);如果數(shù)據(jù)幀被對(duì)方拒絕接收,則停止數(shù)據(jù)的繼續(xù)發(fā)送,并且接收端口和發(fā)送端口通過同步控制幀重新進(jìn)行端口同步,當(dāng)這種同步重新建立后發(fā)送端口才可以繼續(xù)發(fā)送數(shù)據(jù);在發(fā)送狀態(tài)機(jī)模塊中采用了滑動(dòng)窗口技術(shù),一方面可大大提高數(shù)據(jù)的吞吐量;另一方面可以盡量避免由于接收方緩沖區(qū)資源不足而導(dǎo)致的多次發(fā)送失敗。

3.2.2 接收狀態(tài)機(jī)模塊設(shè)計(jì)

當(dāng)接收到數(shù)據(jù)幀后,對(duì)接收到的數(shù)據(jù)幀通過CRC校驗(yàn)機(jī)制進(jìn)行錯(cuò)誤檢查,同時(shí)得到幀的序號(hào)和設(shè)備號(hào)等信息,并且將數(shù)據(jù)幀的接收狀態(tài)通知本地發(fā)送端口,由本地發(fā)送端口根據(jù)接收數(shù)據(jù)的狀態(tài)作出判斷,然后向?qū)Ψ焦?jié)點(diǎn)設(shè)備發(fā)送響應(yīng)幀信號(hào)。

當(dāng)接收狀態(tài)機(jī)接收到一個(gè)完整的消息后,則由接收狀態(tài)機(jī)向本地處理器接口發(fā)出中斷信號(hào),通知處理器將接收緩沖區(qū)內(nèi)的數(shù)據(jù)取出;當(dāng)接收狀態(tài)機(jī)接收到控制幀后,根據(jù)控制幀的類型作出判斷,如果是錯(cuò)誤數(shù)據(jù)的響應(yīng)幀,則本地發(fā)送端口和接收端口同時(shí)處于停止發(fā)送和接收數(shù)據(jù)狀態(tài),并且通知本地發(fā)送端口發(fā)送link請(qǐng)求幀和link相應(yīng)幀,使得接收和發(fā)送鏈路重新建立連接;如果是用于鏈路控制的控制幀,則本地發(fā)送端口根據(jù)接收到的控制幀類型向相鄰節(jié)點(diǎn)發(fā)送相應(yīng)的響應(yīng)控制幀。

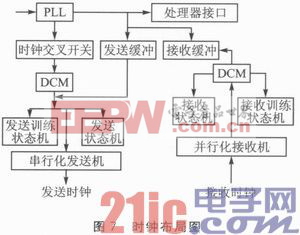

3.3 時(shí)鐘信號(hào)設(shè)計(jì)

RapidIO協(xié)議規(guī)定使用雙數(shù)據(jù)時(shí)鐘發(fā)送和接收數(shù)據(jù)。

在專用電路內(nèi)的時(shí)鐘布局分為發(fā)送時(shí)鐘模塊和接收時(shí)鐘模塊兩大子模塊。對(duì)時(shí)鐘的分頻和倍頻是通過專用集成電路內(nèi)的數(shù)字時(shí)鐘管理器DCM完成的。來自處理器的輸出時(shí)鐘要驅(qū)動(dòng)專用電路芯片和其他外設(shè),所以在專用電路的內(nèi)部加入PLL,保證輸出時(shí)鐘能提供足夠的時(shí)鐘頻率、驅(qū)動(dòng)能力和較陡的時(shí)鐘邊沿。時(shí)鐘資源在專用電路內(nèi)的布局如圖7所示。

發(fā)送時(shí)鐘模塊的主要功能包括:

①使用DCM的相移功能,提供RapidIO發(fā)送數(shù)據(jù)合適的采樣時(shí)鐘相位,包括從發(fā)送緩沖區(qū)將數(shù)據(jù)提取出來,以及在發(fā)送數(shù)據(jù)前提供的較好的冗余時(shí)鐘相位,保證時(shí)鐘能正確地采集發(fā)送的數(shù)據(jù)和幀同步信號(hào)。

②在進(jìn)行數(shù)據(jù)串行化的時(shí)候,通過DCM的倍頻功能將上層模塊的數(shù)據(jù)發(fā)送變成雙數(shù)據(jù)進(jìn)行發(fā)送,即時(shí)鐘的上沿和下沿同時(shí)發(fā)送數(shù)據(jù)。

③通過差分引腳將LVTTL發(fā)送時(shí)鐘變?yōu)長(zhǎng)VDS差分時(shí)鐘進(jìn)行發(fā)送。

接收時(shí)鐘模塊中的主要功能包括:

①接收到的差分LVDS時(shí)鐘轉(zhuǎn)換為L(zhǎng)VTTL時(shí)鐘。

②對(duì)接收到的時(shí)鐘信號(hào)通過DCM對(duì)其進(jìn)行分頻,以便能夠正確地將接收到的DDR數(shù)據(jù)轉(zhuǎn)化為SDR數(shù)據(jù)。

③對(duì)接收到的時(shí)鐘通過DCM進(jìn)行相位移動(dòng),以便為接收緩沖區(qū)正確地接收數(shù)據(jù)提供正確的采樣時(shí)鐘相位。

除了此處提到的模塊,RapidIO協(xié)議專用集成電路內(nèi)部還有串行和并行模塊,接口模塊等,在此就不一一介紹了。

結(jié)語

適用于多核DSP系統(tǒng)的高速互聯(lián)接口對(duì)于研究多核的體系結(jié)構(gòu)具有實(shí)際意義。研制滿足RapidIO協(xié)議的專用集成電路不僅可以快速實(shí)現(xiàn)網(wǎng)絡(luò)結(jié)構(gòu),而且可以降低系統(tǒng)的功耗,提高可靠性,具有很好的應(yīng)用價(jià)值。

評(píng)論