T-MMB系統中LDPC碼譯碼器的FPGA設計與實現

變量節點處理單元(VNU)

本文引用地址:http://www.104case.com/article/146837.htm在LDPC碼的迭代譯碼過程中,變量節點處理單元以加減運算為主,數據以補碼形式表示有利于簡化操作[10],本文實現的VNU流水線結構如圖5所示。圖6表示垂直運算的FPGA運算結果,該模塊的時鐘頻率最高可以達到321.62MHz。

實現結果

在T-MMB系統中,OFDM進行逆快速傅里葉變換的速率為2.048M符號/s。接收端在接收該信號后進行8PSK軟解調,因此軟解調模塊的工作速率需要達到3×2.048MHz即6.144MHz才能滿足系統時序要求。本次設計中軟解調模塊的時鐘頻率可以達到216.16MHz,滿足系統要求。

譯碼器接收信息的速率為6.144MHz,需要能對每一組輸入的軟信息進行正確譯碼,保證在下一組軟信息開始譯碼的時候上一次譯碼已經結束。則譯碼器工作頻率要滿足公式(1)要求。

???????? ![]() ?

?

T為譯碼器的工作周期,N為規定的迭代次數,100+100是為了保證系統性能防止溢出將水平運算次數與垂直運算次數擴大為100。由公式(1)可得到譯碼工作頻率至少為30MHz,而本文實現譯碼器的時鐘頻率可以達到86.38MHz,可以滿足系統對譯碼器時鐘頻率的要求。

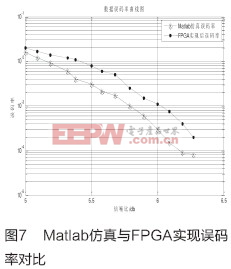

本文首先進行了Matlab浮點運算仿真,之后對譯碼器進行硬件實現。將Matlab中的浮點運算譯碼結果與8比特量化后經FPGA實現的譯碼結果進行對比,對比結果見圖7。

?

?由于FPGA處理定點數據,量化后譯碼性能與浮點數運算譯碼性能有一定的差距,但該性能在可接受的范圍內,能夠滿足系統對譯碼器譯碼性能的要求。

結束語

本文利用QC-LDPC碼的循環結構,采用部分并行結構設計實現了一種高效存儲的譯碼器結構,將偏移量相同的子矩陣對應的校驗節點信息或變量節點信息存儲在相同的塊RAM中。該方法能夠有效減少QC-LDPC碼譯碼器對BRAM資源的需求。基于Xilinx公司Vertex-4系列FPGA的實驗結果表明,本文提出的存儲方法與傳統的存儲方式相比可以節約75%的BRAM資源,實驗還表明采用該方法得到的QC-LDPC碼譯碼器能夠實現較高的系統時鐘頻率,因而能夠達到較大的譯碼吞吐量。

參考文獻:

[1] 新一代地面移動多媒體廣播系統(T-MMB)簡介[J].數字通信世界,2006,(11):44-45

[2] 尹航,胡志強,肖如吾.移動多媒體廣播系統中LDPC編碼器的設計與實現[J].中國傳媒大學學報自然科學版,2009,16,(4):78-84

[3] Gallager R G. Low-density Parity-check Codes[J].IRE Transactions on Information Theory, 1962,2,(8):21-28

[4] MacKay D J C, Cavendish L, Cambridge U. Good Error-correcting Codes Based on Very sparse matrices[C].Proc. IEEE International Symposium on Information Theory.1997:113.

[5] 徐歡,雷菁,文磊.準循環LDPC碼低存儲量譯碼器設計與實現[J].重慶郵電大學學報(自然科學版),2010,22(6):771-774.

[6] Fossorier M P C, Mihaljevic M, Imai H. Reduced complexity iterative decoding of low density parity check codes based on belief propagation[J].IEEE Transactions on Communications,1999,47(5):673-680.

[7] 何慶濤,周正,葛建華.準循環LDPC碼譯碼器的FPGA實現[J].空間電子技術,2009,1:40-102.

[8] 喬華,管武,董明科,等.LDPC碼高速譯碼器的設計與實現[J].北京大學學報(自然科學版),2007,2(2):1-6.

[9] 袁瑞佳,白寶明.基于FPGA的部分并行QC-LDPC譯碼器高效存儲方法[J].通信學報,2012,33(11):165-170.

[10] 張仲明,許拔,楊軍,等.800Mbps準循環LDPC碼譯碼器的FPGA實現[J].信號處理,2010,26(2):255-261.

fpga相關文章:fpga是什么

評論