T-MMB系統中LDPC碼譯碼器的FPGA設計與實現

——

本文設計的高效存儲方式偏移量最多為71,同一種信息對應的子矩陣為224,與傳統存儲方式相比可以節省75%的RAM資源。這種存儲方式不僅減少了塊RAM資源的浪費,也減少了譯碼器實現所需的存儲資源數量。表2對比了傳統存儲方式與改進后的RAM存儲方式資源的占用情況。

本文引用地址:http://www.104case.com/article/146837.htm ?

?主要模塊的硬件實現

針對本文提出的高效存儲譯碼架構,本文在實際的FPGA硬件平臺上進行了譯碼器驗證。下面列舉了主要功能模塊的硬件設計,其中譯碼器的各模塊均采用了多級流水線技術。

?

?校驗節點處理單元(CNU)

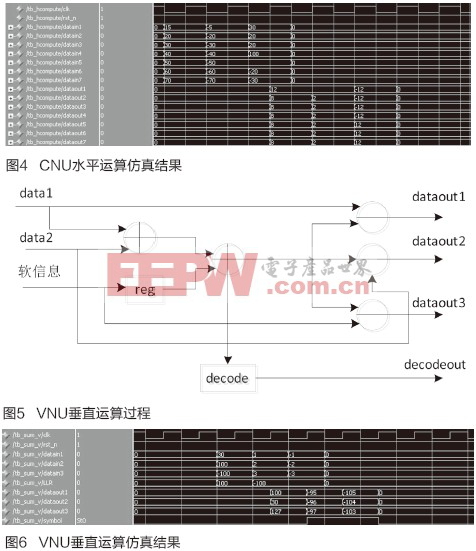

CNU總體被劃分為5級流水線,其結構如圖3所示。乘法電路采用減法及移位操作來代替,從而簡化計算電路。這種運行方式運行在較高的時鐘頻率下,該模塊的最高時鐘頻率可以達到171.73MHz。圖4表示了水平運算的FPGA仿真結果。

?

?fpga相關文章:fpga是什么

評論