T-MMB系統中LDPC碼譯碼器的FPGA設計與實現

摘要:本文設計了一種符合手機電視T-MMB標準的信道譯碼解決方案,并進行了MATLAB仿真和FPGA的實現。同時針對部分并行結構的準循環低密度校驗(QC-LDPC)碼譯碼器,提出了基于塊RAM的高效存儲方法。該方法既可以同時讀取用于運算的校驗節點信息或變量節點信息,又可以實現在同一塊RAM中存儲不同子矩陣對應的校驗節點信息或變量節點信息,不僅避免了塊RAM資源的浪費,而且減少了譯碼器實現所需的存儲資源數量。在Xilinx公司Virtex-4系列的FPGA上的實現結果表明,與傳統的子矩陣與塊RAM一對一存儲的譯碼結構相比,本文提出的QC-LDPC碼譯碼器設計方法能夠在減少塊RAM數量的同時有效地提高系統的時鐘頻率和譯碼吞吐量。

本文引用地址:http://www.104case.com/article/146837.htm引言

隨著移動網絡的迅速發展,移動多媒體廣播業務已經成為炙手可熱的發展熱點。國際上流行的數字移動多媒體廣播標準主要有三個:歐洲的DVB-H,美國的MediaFLO和韓國的T-DMB。而中國在2006年9月,由北京新岸線軟件科技有限公司提出了新一代地面移動媒體廣播(Terrestrial Mobile Multimedia Broadcasting,簡稱T-MMB)系統。該系統具有獨立自主知識產權,相比于其他制式具有頻譜利用率高、復雜度低、功耗小、頻點可用性好、兼容性好等優點[1]。T-MMB系統是基于多載波OFDM調制的無線通信系統,采用LDPC碼作為信道編碼技術,無需級聯外碼就可以保障系統的接收性能,從而提高了系統的頻譜效率,降低接收機復雜度[2]。

低密度校驗(Low-Density Parity-Check,LDPC)碼是一種基于稀疏校驗矩陣的線性分組碼,具有逼近香農極限的譯碼性能[3,4]。準循環低密度校驗(QC-LDPC)碼是低密度校驗碼的一種,其生成矩陣和校驗矩陣都具有準循環的特點,在保持較好譯碼性能的基礎上大大降低了譯碼器實現的復雜度,易于用FPGA實現。LDPC碼譯碼器的研究工作一直是LDPC碼研究的一個重要方向。

LDPC碼的譯碼是一個不斷迭代的消息傳遞過程。譯碼過程中需要存儲大量的信息,包括各節點的初始信息、外信息和后驗信息等[5]。LDPC碼較強的糾錯性能一般是建立在較長碼長基礎上的,這會增加譯碼算法實現過程中的存儲器容量,增加硬件資源成本與開銷[5]。為了有效解決LDPC碼譯碼器的高存儲量問題,本文在QC-LDPC碼基礎上,基于歸一化最小和譯碼算法,設計出一種能夠有效降低存儲量的譯碼器結構,并應用FPGA實現。與傳統的譯碼器相比,本文提出的譯碼器結構能節省75%的存儲空間,同時提升系統的時鐘頻率和譯碼吞吐量。

?

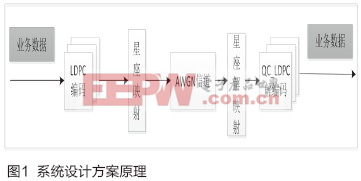

?T-MMB系統的總體設計

本文搭建的T-MMB系統總體架構如圖1所示。按照圖1建模,進行MATLAB仿真并進行譯碼器的FPGA實現。業務數據經過1/2碼率的LDPC碼編碼后,得到調制前的信息序列,其中T-MMB系統中LDPC碼有兩種編碼方式,表1給出了標準中LDPC碼的詳細編碼參數;之后進行8PSK調制,加高斯白噪聲;之后解調得到各碼元對應的軟信息;最后,按照譯碼算法進行譯碼處理,求出誤碼率。本文采用的譯碼算法為歸一化最小和譯碼算法,它是修正最小和譯碼算法中的一種,可以避免譯碼過程中的信道估計,提高譯碼器工作的穩定性[8],其譯碼步驟參考文獻[5]所示。

高效存儲譯碼架構

手機電視標準T-MMB中規定QC-LDPC碼的校驗矩陣維度為2304×4608,可以由32×64個72×72的分循環矩陣構成。每行中不為全0矩陣的個數為7,每列中不為全0矩陣的個數為2、3、9。綜合考慮譯碼器的速率要求和FPGA面積要求,本文采用部分并行結構的運算方式完成譯碼器的設計,采取8bit均勻量化。按照文獻[9]對存儲資源的計算方法可知量化比特數Q=8,部分并行結構譯碼器的復用指數L=72。水平運算時有32個校驗節點處理單元(CNUs)同時運算,需要同時向32×7個存儲變量節點信息的RAM中讀取變量節點信息用于水平運算,計算結果需要同時存儲到32×7個存儲校驗節點信息的RAM中,重復計算72次就可以完成一次迭代中的水平運算。垂直運算時有64個變量節點處理單元(VNUt)在同時運算,向每列中的子矩陣對應的存儲校驗節點信息的RAM同時取出數據進行運算,運算72次后將結果存儲到相應列矩陣對應的存儲變量節點信息的RAM中。

若采用傳統的子矩陣存儲方式,每個子矩陣需對應一個RAM存儲校驗節點信息以及一個RAM存儲變量節點信息,每個RAM寬度為8bit,深度為72。本次設計共需要448個RAM來存儲校驗節點信息以及變量節點信息,需要占用較多的存儲資源,同時由于本設計LDPC碼碼字較長校驗矩陣較大,其余單元在實現時亦需要占用較多的存儲資源,一般的FPGA很難滿足這樣的要求。

本文設計了一種新的RAM存儲方式,采用Xilinx公司Virtex-4系列的FPGA進行實現,采取自帶塊RAM的存儲方式,RAM容量為18Kb。在實現時,將塊RAM例化為寬度32bit深度155的雙口塊RAM,深度0~71上存放校驗節點信息,深度80~151上存放變量節點信息。因為校驗節點與變量節點同時處理的多個消息必須同時讀出或寫入存儲器中[10]。為保證同步,本文采取的做法是將偏移量相同的子矩陣對應的校驗節點信息或變量節點信息存儲到同一塊RAM中。由于Xilinx的塊RAM最大位寬為32bit,所以最多有4個子矩陣對應的信息可以存儲到同一塊RAM中。存儲方式如圖2所示。

?

?fpga相關文章:fpga是什么

評論