中芯與燦芯40LL ARM Cortex-A9測試芯片成功流片

國際領先的IC設計公司及一站式服務供應商—燦芯半導體(上海)有限公司與中芯國際集成電路制造有限公司及ARM日前聯合宣布,采用中芯國際40納米低漏電工藝的ARM Cortex-A9 MPCore 雙核測試芯片首次成功流片。

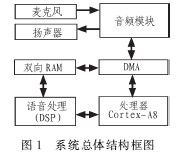

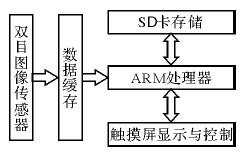

本文引用地址:http://www.104case.com/article/129668.htm該測試芯片基于ARM Cortex-A9雙核處理器設計,采用了中芯國際的40納米低漏電工藝。處理器使用了一個集32K I-Cache和32K D-Cache,128 TLB entries,NEON 技術,以及包括調試和追蹤技術的CoreSight 設計套件。除高速標準單元庫,該測試芯片還采用高速定制存儲器和單元庫以提高性能。設計規則檢測之簽核流程(sign-off)結果已達到900MHz(WC),預計2012年第二季度流片結束后,實測結果將達到1.0GHz。

燦芯半導體總裁兼首席執行官職春星博士指出:“ARM Cortex-A9雙核測試芯片采用了中芯國際的40納米低漏電工藝,大幅縮短了整個芯片設計時間,并且降低了開發成本與流片風險,這一系列工藝技術和設計上的優化措施將推動高性能的Cortex-A9處理器快速面市。我們很高興在處理器內核及其優化實現上與ARM及中芯國際建立緊密的合作伙伴關系,該測試芯片的順利流片再次證明了三家公司合作的成功。有了ARM和中芯國際的支持,我們必將為需要高性能ARM內核的客戶帶來巨大價值。”

中芯國際首席商務長季克非表示:“通過與ARM和燦芯的密切合作,中芯國際能夠為客戶提供一個快速實現從設計到生產的完整平臺。我們十分重視與燦芯、ARM的合作伙伴關系。也正因為他們的努力,我們才能達成此40納米技術的重要里程碑,這對我們‘為客戶提供最先進的制程技術’的共同承諾是最有力的證明。中芯國際40納米技術結合ARM Cortex-A9處理器和燦芯的設計流程,將有助于滿足高性能和低功耗消費電子產品日益增長的需求。”

ARM中國區總裁吳雄昂說:“在中國,ARM堅持致力于與合作伙伴共同努力,創造一個推動創新與成長的生態系統。這個與燦芯半導體、中芯國際共同創造的重要里程碑,證明了通過我們的合作,可以承諾并最終實現以高性能、低功耗的產品,來更快地滿足市場不同領域的需求。”

pic相關文章:pic是什么

漏電開關相關文章:漏電開關原理

評論