賽靈思SSI技術為FPGA帶來全新密度、帶寬和功耗優勢

將堆疊硅片互聯技術投入生產

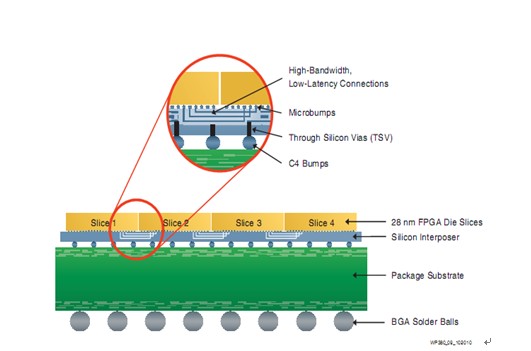

本文引用地址:http://www.104case.com/article/127574.htm結合使用硅通孔技術與受控的塌落芯片連接 (C4) 焊錫凸塊,賽靈思得以將 FPGA/中介層堆疊用倒裝片組裝技術貼裝到高性能封裝基片上(如圖6 所示)。這種大節距硅通孔為并行和串行 I/O,電源/接地、時鐘、配置信號等提供了封裝和 FPGA 之間的連接。

圖 6:封裝基片

由多項正在申請專利的創新堆疊硅片互聯技術能夠通過超過 10,000 個器件規模的連接提供每秒數 Tb 的芯片間帶寬,足以滿足最復雜的多芯片設計需求。賽靈思采用該新技術開發的 Virtex®-7 FPGA 系列具有無與倫比的功能,其中包括:200 萬個邏輯單元、65 Mb block RAM、2,375 GMACS 的 DSP 性能(4,750 GMACS 用于對稱濾波器)、1,200個支持1.6Gb/s LVDS并行接口的 SelectIO 引腳、以及72個能夠提供 1,886Gb/S 雙向總帶寬的串行收發器。

將堆疊硅片互聯技術投入生產

賽靈思在采用堆疊硅片互聯技術開發 FPGA 的開發策略是從廣泛建模以及一系列用于設計實現、可制造性驗證和可靠性評估的測試器件(或測試平臺)的創建開始的。

應力仿真模型還顯示出堆疊硅片技術的另一項優勢。與單片解決方案相比,硅中介層起到了緩沖作用,降低了低介電電介質應力,并提升了 C4 凸塊的可靠性。

對堆疊芯片進行的廣泛的熱效應仿真顯示,采用堆疊硅片互聯技術的器件的熱性能可與單片器件相媲美。

經過與業界領先的供應商五年多的共同研發,以及在一系列多種測試平臺上的廣泛測試,賽靈思首批采用堆疊硅片互聯技術的 FPGA可以 順利走向量產。這些測試平臺主要用于工藝模塊開發與集成、可靠性評估、供應鏈確認、設計實現、中介層裸晶良品測試 (KGD) 以及微凸塊電遷移 (EM) 規則驗證等。

迄今為止,通過測試平臺成功完成的可靠性測試包括:

- 硅通孔、C4 焊球和中介層互聯通過了 1000 個周期的封裝級和晶圓級 Cycle B溫度 測試;

- 微凸塊結點通過了 1000 小時的高溫存儲測試;

- 測試結果顯示微凸塊結點的電遷移累積密度函數 (CDF) 為 0.1%。

賽靈思擁有穩健可靠的技術供應鏈,為生產業界首批采用堆疊硅片互聯技術的 FPGA 做好了充分準備。TSMC、Ibiden、等相關合作伙伴將充分利用他們的資源和技術專長,共同生產 28nm FPGA 和 65nm 硅中介層、互聯層、微凸塊、C4焊球和封裝基片,并進行晶圓減薄、芯片分離、疊層芯片連接和封裝組裝等工序。

評論