賽靈思SSI技術為FPGA帶來全新密度、帶寬和功耗優勢

——

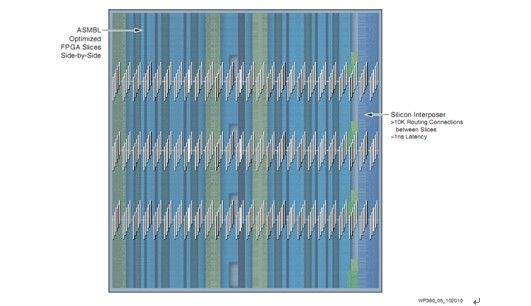

從基本的 ASMBL 架構出發,賽靈思已經推出了實現堆疊硅片集成的三項重大改進(如圖3 所示)。首先,每個芯片 Slice 接收自己的時鐘和配置電路。其次,對走線架構進行了改進,通過對芯片進行表面鈍化處理,實現了 FPGA 邏輯陣列內部布線資源的直接連接,繞開了傳統的并行和串行 I/O 電路。第三,對每個芯片 Slice 進行進一步加工,形成微凸塊,以便將芯片連接到硅基片上。與采用傳統 I/O 相比,正是這項創新使連接的數量大幅增加,同時又顯著降低了時延和功耗(與標準 I/O 相比,單位功耗芯片間連接功能提高了 100 倍)。

本文引用地址:http://www.104case.com/article/127574.htm

圖 3:針對硅片堆疊集成進行優化的 FPGA 芯片 Slice

硅通孔技術實現硅中介層

無源硅中介層負責 FPGA 芯片的互聯。它采用風險低、良率高的 65nm 工藝技術制造而成,擁有四個金屬化層,以構建用以連接多 FPGA 芯片的邏輯區的成千上萬條跡線。(如圖 4 所示)

圖 4:無源硅中介層

圖5是已經組裝完成的芯片堆疊的“X 光透視圖”。它在無源硅中介層上并行放置了四個堆疊的FPGA芯片(底視圖)。通過透明顯示,可以觀察到用硅中介層上的走線連接起來的 FPGA 芯片 Slice(未縮放)。

圖5:組裝完成的芯片堆疊的“X光透視圖”

評論