將ARM AXI4用于FPGA 把恒星裝入瓶中

本文引用地址:http://www.104case.com/article/127296.htm

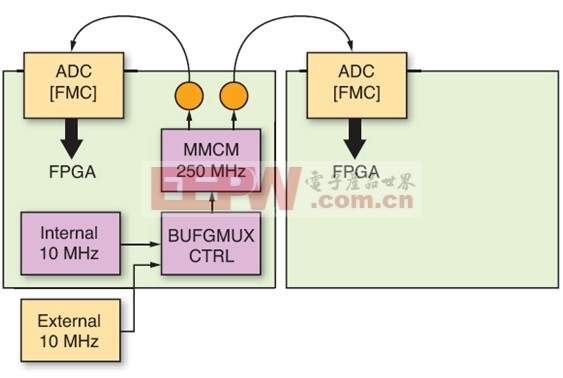

圖 4:兩個 FPGA 板必須精確同步,圖中的時鐘原理可以確保這種一致性。

外部 10MHz 時鐘按同樣的方式完成時鐘信號到達、發送、再回到兩個 ADC 的過程,也就是說,外部觸發采用與內部時鐘相同的方法來確保兩塊板都能夠實現同步觸發。

獨特的性能帶來的優勢

我們在設計中充分利用了賽靈思 FPGA 架構提供的一些新穎的功能。例如,我們使用IODELAY 原語在引腳上調整路徑時延,這樣我們就能夠補償走線長度的差異。這項功能非常重要,因為從 ADC 到 FMC 的數據路徑長度不等。如果我們不補償路徑時延,ADC 輸出的數據就是無用數據。ADC 輸出的數據在 250MHz 時鐘下以雙倍的速率輸出,因此有效數據單元之間的時間間隔僅有 2ns。IODELAY 可以讓我們按 125ps 的步長非常精確地調整數據路徑。

同樣重要的是混合模式時鐘管理器 (MMCM),它的作用是執行諸如乘法和相移等時鐘管理任務。在級聯模式下,即把一個 MMCM 與另一個相連,我們可以使用原始的 10MHz 時鐘生成多種時鐘。這其中就包括 250MHz 的 ADC 采樣時鐘以及我們用于其它目的的其它時鐘。

圖 5:FPAG 數據采樣盒由賽靈思的 ML605 評估板、4DSP 的 FMC108 ADC 板和我們自己開發的 FMC/PMOD 插頭板組成。我們把 ADC SSMC 接插件在內部連接到前板上的 SMA 隔板上,以延長 ADC 模擬連線的壽命。

我們還充分發揮 BUFGMUX_CTRL 和 IDDR 原語的作用。由于我們的系統需要在內部時鐘和外部 10MHz 時鐘之間切換,非常重要的是這種切換不得產生脈沖。運用 BUFGMUX_CTRL原語可以保證這一點。該原語還可用于標準邏輯,比如觸發器(不一定是用于時鐘的)。但是需要將屬性 IGNORE0、IGNORE1 設置為 1,以繞開去脈沖電路,否則邏輯不能通過。

評論