將ARM AXI4用于FPGA 把恒星裝入瓶中

很明顯,我們需要對設計進行深層研究。我們的解決方案是采用自主開發的 FireStark 協議,它是一種基于 UDP 的協議,位于 AXI 以太網 DMA 驅動程序內部。通過調整 MicroBlaze Linux 內核驅動程序和把 FPGA 放在專用網絡上,我們現在能夠在 60 秒內完成對整個 2Gb 數據的下載,速度提高 70 倍。如果使用高達 6Kb 的巨型幀進行測試,速度還可以翻倍,即超過 70Mb/s。關鍵之處在于,這說明使用 DMA,即便是在較慢的 100MHz 的 MicroBlaze 時鐘下,也能夠在存儲器和網絡之間實現極高的數據吞吐能力。

本文引用地址:http://www.104case.com/article/127296.htm

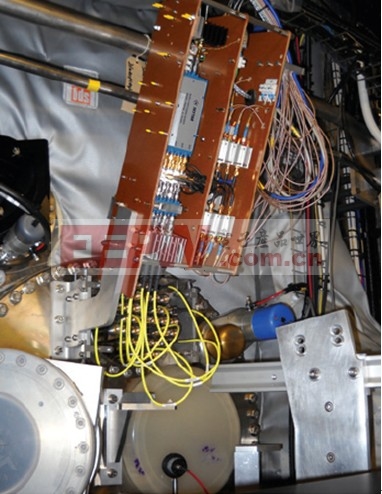

圖 3:連接到 MAST 托卡馬克裝置的 RF 電子設備能夠將接收到的 6GHz 至 40GHz 的信號降頻為 250MHz 帶寬信號,供 FPGA 數據采集盒處理。

FPGA 到 PC 機的時延經測量為 129µs +/- 13µs(真正的時延會更低,因為該測量值包含數據包穿越交換機、通過 PC 內核、到達網絡堆棧以及最終進入用戶區域的時延)。我們還準備測量 FPGA 之間的時延,預計會更低。

時鐘同步

我們的托卡馬克裝置有許多診斷裝置和系統,它們都需要同步為 10MHz 的全局實驗時鐘。我們從這個時鐘信號中派生出 250MHz 的數據采集時鐘,同時這個派生出的信號還為 ADC 板提供時鐘。剩余的 FPGA 邏輯則由板載晶振時鐘來驅動。

我們的系統有一個特別的地方,就是不會連續發送實驗時鐘,只在有觸發事件的時候發送大約 10 秒鐘。在此期間之外,我們需要切換到內部生成的時鐘。因此我們需要在兩個時鐘之間來回切換,即在外部時鐘和內部時鐘間切換。

對兩個 FPGA 板有一個重要要求,就是它們必須精確同步。在理想情況下,我們的采樣周期為 4ns,那么在所期望的最高頻率下 ADC 的可讀輸入正弦的周期為 8ns,相當于 360 度。如果我們需要 5 度的相位精度,我們能夠容忍的最大歪斜為8X (5/360)=111ps。這種程度的精度很難實現,因為即便是光在這么短的時間內也只能行進 3.3cm。

我們為兩塊板子設計的固件完全相同。我們使用 DIP 開關來啟用或者停用每塊板子需要的不同功能。這樣可以大幅度地節省開發時間,因為我們只需要對固件進行一次綜合。

時鐘由兩塊板中的一塊生成,然后通過兩個臨近的 SMA 端口輸出,隨后反饋到與每塊 FPGA 板的 FMC 端口相連的 ADC 板(使用相等長度的線纜)。這樣可以保證每塊板都能夠精確地運行在相同的時鐘上,唯一的相位差是信號離開 FPGA 板時兩個 SMA 端口之間的相位差。圖 4 更加清楚地說明了這種設計方法。

評論