富士通與SuVolta展示其SRAM可在0.4伏低壓下工作

—— 這些技術降低能耗為即將出現的終極“生態”產品鋪平道路

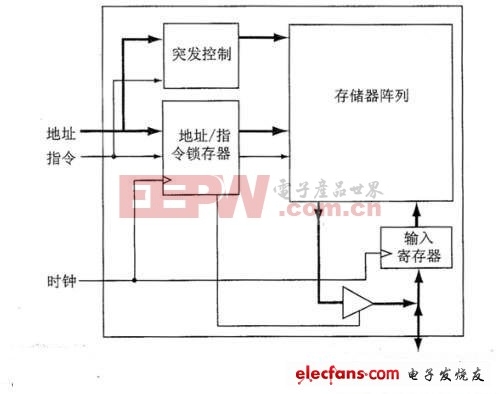

富士通半導體有限公司和SuVolta公司宣布,通過將SuVolta的PowerShrink 低功耗CMOS與富士通半導體的低功耗工藝技術集成,已經成功地展示了在0.425V超低電壓下,SRAM(靜態隨機存儲)模塊可以正常運行。這些技術降低能耗,為即將出現的終極“生態”產品鋪平道路。技術細節和結果會在12月5日開始在華盛頓召開的2011年國際電子器件會議(IEDM)上發表。

本文引用地址:http://www.104case.com/article/126853.htm從移動電子產品到因特網共享服務器,以及網絡設備,控制功耗成為增加功能的主要限制。而供應電壓又是決定功耗的重要因素。之前,CMOS的電源電壓隨著器件尺寸減小而穩定下降,在130nm技術結點已降至大約1.0V。但在那之后,技術結點已縮小到28nm,電源電壓卻沒有隨之進一步降低。電源供應電壓降低的最大障礙是嵌入的SRAM模塊最低工作電壓。

結合SuVolta的Deeply Depleted Channel™ (DDC)晶體管技術 – 該公司的PowerShrink™平臺組件之一 – 與富士通半導體的尖端工藝,兩家公司已經證實通過將CMOS晶體管臨界電壓(VT)的波動降低一半,576Kb的SRAM可在0.4伏附近正常工作。該項技術與現有設施匹配良好,包括現有的芯片系統(SoC)設計布局,設計架構比如基體偏壓控制,以及制造工具。

評論