SuVolta發布Deeply Depleted Channel技術

致力于開發可微縮低功耗CMOS技術的公司SuVolta今日在2011年IEDM會議上發布其Deeply Depleted Channel (DDC - 深度耗盡通道)的技術細節。SuVolta的DDC技術是該公司的PowerShrink低功耗CMOS平臺的組成部分。該低功耗技術已向業界證明可以在不影響速度的前提下降低功耗百分之五十。配合先進的電壓降低手段,DDC技術甚至可以降低功耗達百分之八十或更多。

本文引用地址:http://www.104case.com/article/126723.htmSuVolta總裁兼首席執行官Bruce McWilliams博士稱:“SuVolta的技術已經由實際芯片驗證,在半導體工業界引起強烈反響。現在我們披露DDC晶體管技術細節,以便業界專家可以了解SuVolta的技術如何降低功耗,允許低電壓運作,以及實現工藝微縮至20納米以下。”

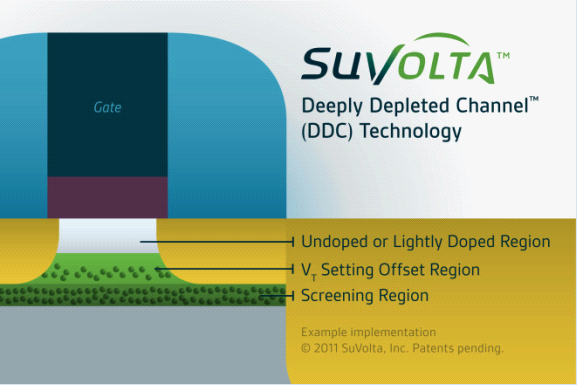

SuVolta Deeply Depleted Channel (DDC)晶體管技術

SuVolta的DDC晶體管降低閾值電壓波動,以實現持續的CMOS微縮。該結構在門極加偏壓時形成深度耗盡通道。在典型應用中,DDC通道包括幾個部分:未摻雜或輕度摻雜區,VT設定區以及屏蔽區。不同應用中SuVolta的DDC晶體管會取決于芯片加工廠或特定芯片設計要求而略有不同。

未摻雜或輕度摻雜區去除通道中的雜質以形成深度耗盡通道。這將減小隨機雜質波動(RDF)從而實現降低VDD,并提高載流子遷移率以增加有效電流。

VT設定區設定晶體管閾值電壓而不影響載流子遷移率。該區也將改善傳統晶體管的VT分布。

屏蔽區起屏蔽電荷并設定耗盡層深度的作用,并且其基體效應使得在需要的時候通過偏壓動態調節VT成為可能。

DDC晶體管通過降低工作電壓來實現低功耗運行。通過控制VT波動,使用SuVolta DDC技術設計的芯片將獲益良多,包括:

· 工作電壓降低百分之三十而不影響效能;

· 大幅降低漏電流;

· 減少設計“保護頻帶”;

· 提升良率。

此外,DDC晶體管允許設定多重VT,這對當今低功耗產品至關重要。除了顯著降低VT波動所帶來的優勢,DDC晶體管還具備其他優點,可以在高速運作中進一步降低功耗。這些優點包括:

· 提高通道載流子遷移率從而增加驅動電流;

· 減小漏極引發勢能降低(DIBL);

· 提高基體效應系數以實現更佳VT控制。

SuVolta公司首席技術長Scott Thompson博士指出:“有些時候單純減小芯片尺寸并沒有太大意義。光刻成本的增加導致每只晶體管成本飽和,正在終結摩爾定律。我相信目前的28nm和20nm將會是長期的技術結點。除了微處理器,移動市場的大多數芯片都更看重成本控制和低功耗。SuVolta的DDC結構獨特之處在于它是唯一的可與現有CMOS工藝集成以及制造設備完全兼容的晶體管方案,使得半導體公司可以保持他們已有的電路知識產權。”

Kleiner Perkins Caufield & Byers合伙人Bill Joy表示:“工業界如果想持續發展移動電子產品,必須提升核心技術。SuVolta發明了基于平面基體CMOS工藝的突破性技術,用于解決半導體工業界最大的挑戰 – 功耗”

評論