基于FPGA的PPM系統設計與實現

/*to detect the position of the

本文引用地址:http://www.104case.com/article/113812.htmshortest pulse*/

module shortest_pulse_det

(clk,ppm_in,dout) ;

input clk,ppm_in;

output dout;

reg dout;

reg temp1,temp2,temp4;

wire temp3;

always @ (posedge clk)

begin

temp1<=ppm_in;

temp2<=temp1;

end

assign temp3=temp2&ppm_in;

always @ (posedge clk)

begin

temp4<=temp3;

dout<=temp4;

end

endmodule

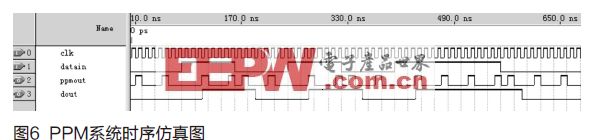

時序仿真

對上述調制與解調模塊的頂層原理圖互聯后,在QuartusII平臺下選擇了Cyclone系列芯片EP1C3T100C6,運行時序仿真后得到整機系統的時序仿真圖如圖6所示。

通過圖6,可以發現該PPM系統的調制與解調部分均滿足要求,有著較好的性能。其中輸出比特流(dout)相對于輸入比特流(datain)有一定的延遲,這個延遲來源于兩個方面,一是系統設計中的整形模塊等所引入的延遲,二是布局布線后器件及連線的固有延遲。同時通過查看綜合報告,得知整機系統總共使用了14個LE,對邏輯資源的消耗較少。

結語

本文提出的基于FPGA的PPM系統的設計方案,在用簡明的Verilog HDL代碼實現后,對FPGA的邏輯資源消耗較少,而且電路性能較好,時序仿真結果證明了上述結論。對實際通信中PPM系統的應用具有一定的參考價值。在民用飛機機載設備S模式應答機的應答信號的傳輸過程中,采用的正是PPM體制,筆者將參考本文的設計方案,并做適當的修改,驗證其是否可用于S模式應答機的空地數據鏈中。

fpga相關文章:fpga是什么

分頻器相關文章:分頻器原理

評論