基于FPGA的PPM系統(tǒng)設計與實現(xiàn)

摘要:給出了脈沖位置調制(PPM)系統(tǒng)的設計方案,并基于FPGA通過簡明的Verilog代碼實現(xiàn)了該設計,時序仿真結果驗證了所設計的系統(tǒng)能夠滿足PPM系統(tǒng)的要求,并在滿足一定性能需求的情況下消耗了較少的邏輯資源。

本文引用地址:http://www.104case.com/article/113812.htm引言

作為一種新型的通信技術,脈沖位置調制(PPM)系統(tǒng)依靠其編碼簡單、傳輸效率高等優(yōu)點,已廣泛應用于超寬帶移動通信、光通信、機載設備的空地數(shù)據鏈等諸多領域,同時PPM信號的調制和解調對整個通信系統(tǒng)的性能影響很大。

本文主要介紹了在QuartusII集成開發(fā)環(huán)境下,充分發(fā)揮數(shù)字設計的優(yōu)勢[1],利用Verilog HDL實現(xiàn)PPM系統(tǒng),并通過時序仿真結果來驗證設計方案。

PPM系統(tǒng)設計

PPM是利用脈沖的相對位置來傳遞信息的一種調制方式,其基本原理就是將碼元信息表示在一個幀時間段內的某個時隙上,若一個碼元由n比特組成,該幀時間段含M個長度為t的時隙,則2^n=M。將n比特位編碼后對應成某個時隙上的脈沖來傳輸該碼元信息,而該幀時間段內的其他時隙上則無脈沖,從而產生PPM信號。通常幀時間段還包含一個保護時間間隔Tp ,則系統(tǒng)的比特率為n/(M×t+Tp)。圖1即為一幀16-PPM信號示意圖,其中的脈沖則表示了當前碼元(0111)所對應的時隙。

PPM系統(tǒng)的主要原理相對簡單,所以可將重點放在代碼編寫和系統(tǒng)實現(xiàn)方面。設計過程中最重要的是各個模塊之間的接口設計,競爭冒險現(xiàn)象的避免等。

為透徹理解PPM系統(tǒng)原理及其本質,簡化PPM系統(tǒng)的設計,故在本文所設計的PPM系統(tǒng)中暫不考慮保護時間間隔Tp,同時取M=4,即設計一個4-PPM系統(tǒng),以便于通過仿真來驗證系統(tǒng)性能。

調制系統(tǒng)

通過上述原理介紹,可知PPM信號的調制實際上是一個計數(shù)輸出脈沖的過程[2],對時隙信號進行計數(shù),當它跟調制數(shù)據相等時就在相應的時隙輸出高電平“1”,其他時隙均輸出低電平“0”。

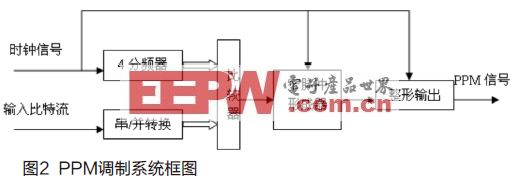

圖2是PPM調制系統(tǒng)的框圖,主要由串/并轉換、4分頻器、比較器、窄脈沖形成器、整形輸出等5個模塊。其中,串/并轉換模塊主要完成對輸入比特流的二進制編碼[3];4分頻器用于生成幀時間段內的4個時隙;比較器完成對上述兩模塊輸出的高低對應位的匹配比較;窄脈沖形成器用于對比較器的輸出做成型濾波,限制PPM脈沖的帶寬,從而減小該PPM脈沖對相鄰頻帶內信號造成的干擾;整形電路僅用D觸發(fā)器實現(xiàn),主要功能是鎖存PPM窄脈沖,與時鐘同步,從而避免競爭冒險現(xiàn)象[3~4]。

解調系統(tǒng)

在設計PPM解調系統(tǒng)時,考慮到PPM信號的產生原理,不難發(fā)現(xiàn)當輸入比特流為連續(xù)的“1”串或連續(xù)的“0”串時,PPM信號脈沖的間隔保持恒定,為4個時鐘周期。而只有在輸入比特流從“1”變?yōu)?ldquo;0”或者從“0”變?yōu)?ldquo;1”時,PPM信號脈沖的間隔才會發(fā)生變化[5]。所以可根據接收到的PPM信號脈沖間隔的不同來完成解調,判斷原輸入比特是“1”還是“0”。

根據上述解調模型,可設計PPM解調系統(tǒng)框圖如圖3所示,主要由時鐘提取電路、脈沖位置檢測電路、譯碼器、整形輸出等模塊構成。其中,時鐘提取電路包括時隙同步[6]、幀同步和字同步[7]等,為簡單起見,在本設計中省略了時鐘提取模塊。脈沖位置檢測電路主要包括最短脈沖位置檢測、最長脈沖位置檢測。值得注意的是,在檢測最短脈沖位置時,需要移位兩個時鐘周期后再和原PPM信號相與才能判別出其位置,這是因為當數(shù)據信號從“1”變?yōu)?ldquo;0”的過渡階段,表示“1”的PPM信號前沿和表示“0”的PPM信號前沿間距為2個時鐘周期。同樣,整形輸出模塊也是依靠觸發(fā)器來鎖存數(shù)據,完成整形。

fpga相關文章:fpga是什么

分頻器相關文章:分頻器原理

評論