Cadence針對28納米工藝為TSMC模擬/混合信號設計參考流程1.0版提供廣泛支持

全球電子設計創新領導廠商Cadence設計系統公司今天宣布,支持臺灣積體電路制造股份有限公司 (以下簡稱TSMC) 模擬/混合信號(以下簡稱AMS)設計參考流程1.0版,以實現先進的28納米工藝技術。Cadence與TSMC在這項全新設計參考流程上的合作,將可協助促進高級混合信號設計的上市時間,幫助降低在設計基礎架構的多余投資,并提高投資回報率。

本文引用地址:http://www.104case.com/article/110542.htm“與Cadence之間的合作伙伴關系,是客戶實現高級模擬/混合信號設計成功不可或缺的一環,”TSMC設計方法與服務行銷副處長Tom Quan說。“針對28納米工藝的TSMC 模擬/混合設計參考設計流程,藉由運用最新工藝技術的優勢,推出目前業界最完整的設計、檢驗與生產芯片的方法學。我們非常樂于與Cadence公司以及整個TSMC開放創新平臺 (Open Innovation Platform™) 生態系統繼續合作,以確保我們的技術能夠跟上新興設計挑戰的腳步,讓我們的客戶在設計基礎架構方面的投資發揮最大價值。”

這個設計參考流程強化為設計團隊提供強大的輔助,幫助他們完成高效、低成本芯片實現的任務,可稱為Cadence EDA360戰略的主要支柱。

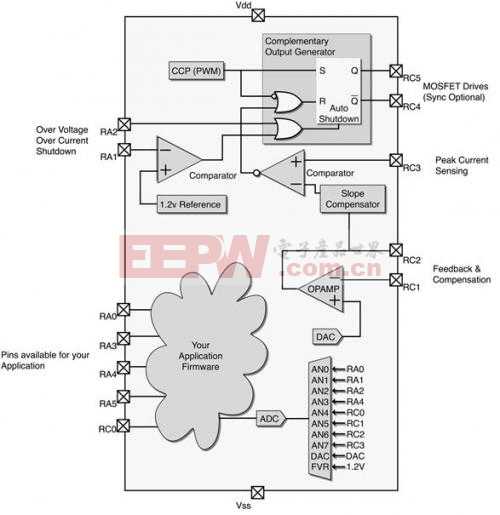

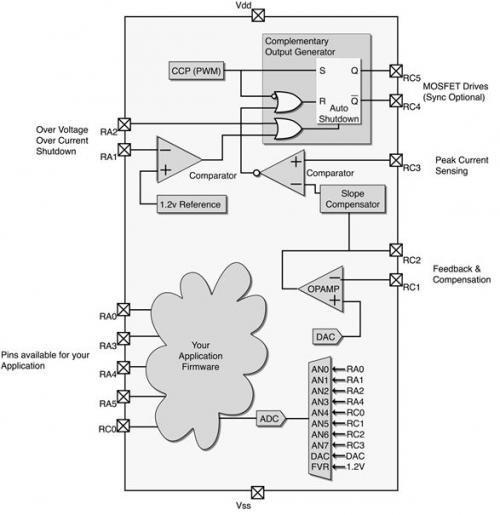

Cadence公司混合信號技術為TSMC嶄新的28納米設計參考流程提供非常全面的產品支持,一步步協助設計邁向芯片實現。Cadence公司與TSMC的合作解決當今在無線、網絡、消費電子與其它應用方面, 芯片設計中模擬與混合信號功能方面越來越高的復雜性與集成度。

“隨著無線、網絡、消費電子與CPU設計復雜度的日益增加,模擬與混合信號IP可以占到芯片設計的50%以上,”產品管理部門主管Sandeep Mehndiratta說。“Cadence支持的TSMC模擬/混合信號設計參考流程1.0版,專為TSMC芯片技術而優化化,為客戶提供全面的設計、驗證與設計實現解決方案,幫助他們在28納米工藝節點上實現高級混合信號設計的最高質量。”

TSMC設計參考流程融合來自Virtuoso平臺的各種Cadence技術陣容,涵蓋在28納米工藝的AMS IP設計、驗證與設計實現。在先進28納米設計經驗證的技術基礎上,Cadence 與TSMC合作,原理圖設計、AMS驗證、射頻與瞬態噪聲分析、良品率靈敏度分析、約束導向型布局、模擬布置與布線、物理驗證、DFM感知的寄生提取、IR壓降與電遷移分析。

評論