利用低端柵極驅(qū)動器IC進(jìn)行系統(tǒng)開發(fā)

在驅(qū)動同步整流器時,驅(qū)動器和功率開關(guān)之間的串聯(lián)柵極電阻往往被忽略,但在實際中常常使用2到20歐姆的這樣一個電阻,原因有三:第一,可抑制功率開關(guān)柵極電容和柵極驅(qū)動回路漏電感之間的振鈴電流,如圖3所示,因為過多的振鈴電流會增加EMI,并因快速切換開關(guān)而增加損耗。其次,可減慢開關(guān)速度,從而降低EMI,不過會導(dǎo)致更高的開關(guān)損耗。第三個可能的原因是,使用一個串聯(lián)柵極驅(qū)動電阻可以把驅(qū)動器的柵極驅(qū)動損耗部分轉(zhuǎn)移到該外接電阻上,而總的柵極驅(qū)動損耗保持不變。

本文引用地址:http://www.104case.com/article/101082.htm

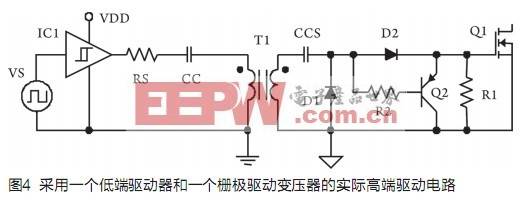

對于具有控制良好的輸入閾值的驅(qū)動器IC,可以利用串聯(lián)電阻外加驅(qū)動器輸入端的小接地電容,在控制路徑上插入固定延時。如圖4所示,在增加?xùn)艠O驅(qū)動變壓器和若干其它元件之后,低端驅(qū)動器還可以用于驅(qū)動高端(浮動)開關(guān),作為高壓驅(qū)動器IC的一種替代方案。這么做的主要原因是,越過隔離邊界,縮短傳播延遲,實現(xiàn)更穩(wěn)健的驅(qū)動電路。

熱設(shè)計

由于驅(qū)動器IC的功耗相當(dāng)顯著,故應(yīng)該關(guān)注熱設(shè)計問題。這是一個兩步過程:首先估算驅(qū)動器的功耗,然后計算結(jié)溫,確保其在設(shè)計限制范圍內(nèi)。對于這里討論的簡單柵極驅(qū)動電路(控制驅(qū)動和非諧振),與功率MOSFET或IGBT每周期開/關(guān)有關(guān)的總柵極驅(qū)動損耗可從開關(guān)的資料表給出的總柵極電荷曲線求得,即讀取對應(yīng)所選柵極驅(qū)動電壓VDD的總柵極電荷Qg,然后按下式計算:

![]()

評論