GPIO詳解-以STM32F103 為例

GPIO是通用輸入/輸出端口的簡稱,是STM32可控制的引腳。GPIO的引腳與外部硬件設備連接,可實現與外部通訊、控制外部硬件或者采集外部硬件數據的功能。

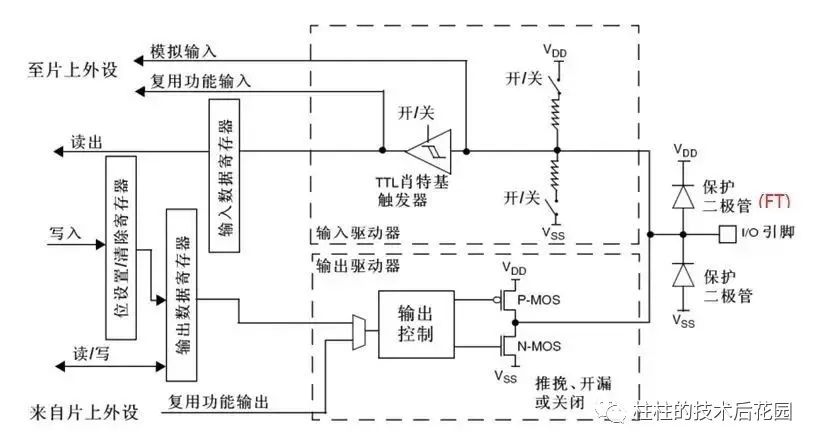

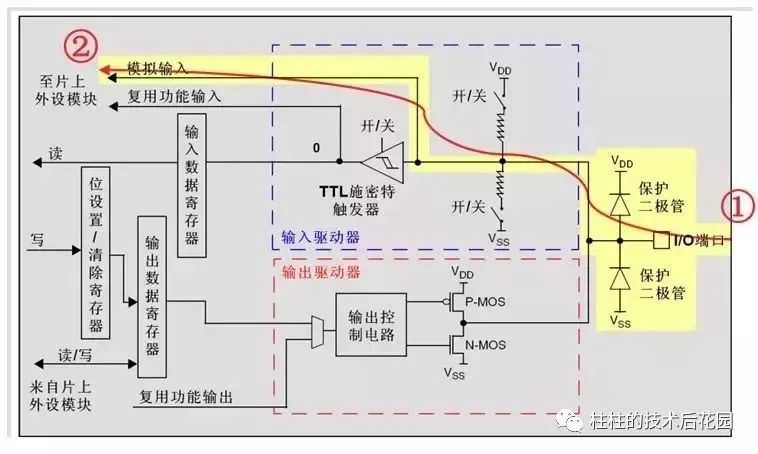

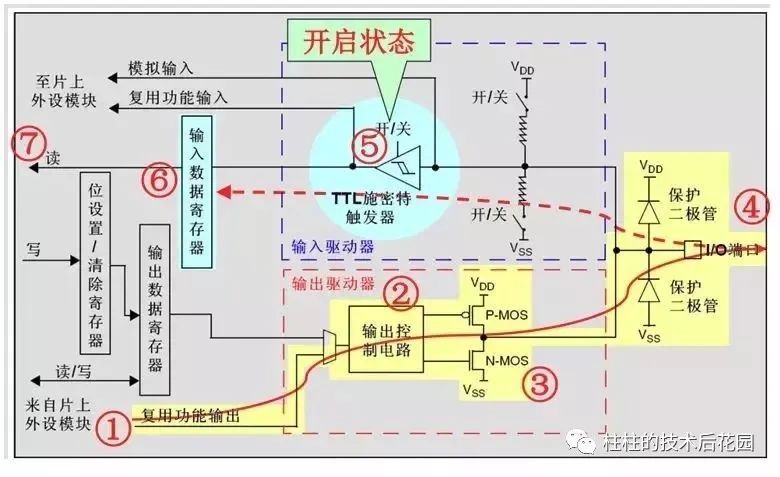

STM32F103ZET6芯片為144腳芯片,包括7個通用目的的輸入/輸出口(GPIO)組,分別為GPIOA、GPIOB、GPIOC、GPIOD、GPIOE、GPIOF、GPIOG,同時每組GPIO口組有16個GPIO口。通常簡略稱為PAx、PBx、PCx、PDx、PEx、PFx、PGx,其中x為0-15。STM32的大部分引腳除了當GPIO使用之外,還可以復用為外設功能引腳(比如串口),這部分在【STM32】STM32端口復用和重映射(AFIO輔助功能時鐘) 中有詳細的介紹。2 簡介2.1 GPIO內部結構

幾點需要注意的地方:

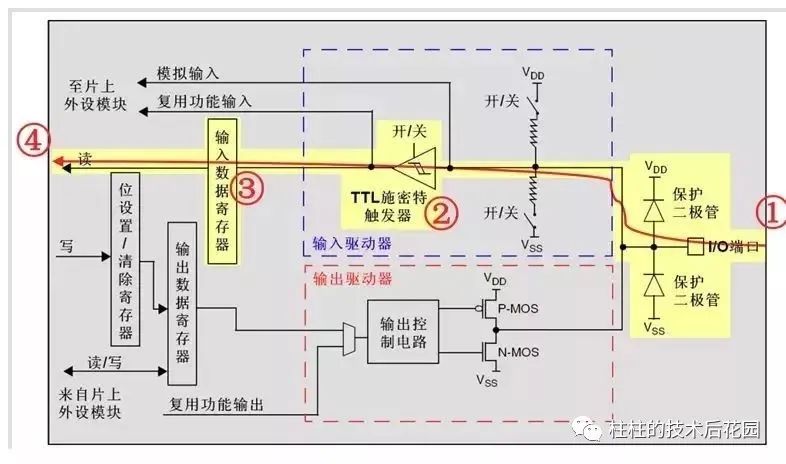

1. 保護二極管:IO引腳上下兩邊兩個二極管用于防止引腳外部過高、過低的電壓輸入。當引腳電壓高于VDD時,上方的二極管導通;當引腳電壓低于VSS時,下方的二極管導通,防止不正常電壓引入芯片導致芯片燒毀。但是盡管如此,還是不能直接外接大功率器件,須加大功率及隔離電路驅動,防止燒壞芯片或者外接器件無法正常工作。

2. P-MOS管和N-MOS管:由P-MOS管和N-MOS管組成的單元電路使得GPIO具有“推挽輸出”和“開漏輸出”的模式。這里的電路會在下面很詳細地分析到。3. TTL肖特基觸發器:信號經過觸發器后,模擬信號轉化為0和1的數字信號。但是,當GPIO引腳作為ADC采集電壓的輸入通道時,用其“模擬輸入”功能,此時信號不再經過觸發器進行TTL電平轉換。ADC外設要采集到的原始的模擬信號。這里需要注意的是,在查看《STM32中文參考手冊V10》中的GPIO的表格時,會看到有“FT”一列,這代表著這個GPIO口是兼容3.3V和5V的;如果沒有標注“FT”,就代表著不兼容5V。2.2 GPIO工作模式

GPIO支持4種輸入模式(浮空輸入、上拉輸入、下拉輸入、模擬輸入)和4種輸出模式(開漏輸出、開漏復用輸出、推挽輸出、推挽復用輸出)。同時,GPIO還支持三種最大翻轉速度(2MHz、10MHz、50MHz)。

每個I/O口可以自由編程,但I/O口寄存器必須按32位字被訪問。GPIO_Mode_AIN 模擬輸入

GPIO_Mode_IN_FLOATING 浮空輸入

GPIO_Mode_IPD 下拉輸入

GPIO_Mode_IPU 上拉輸入

GPIO_Mode_Out_OD 開漏輸出

GPIO_Mode_Out_PP 推挽輸出

GPIO_Mode_AF_OD 復用開漏輸出

GPIO_Mode_AF_PP 復用推挽輸出

3.1 輸入模式

3.1.1 浮空輸入

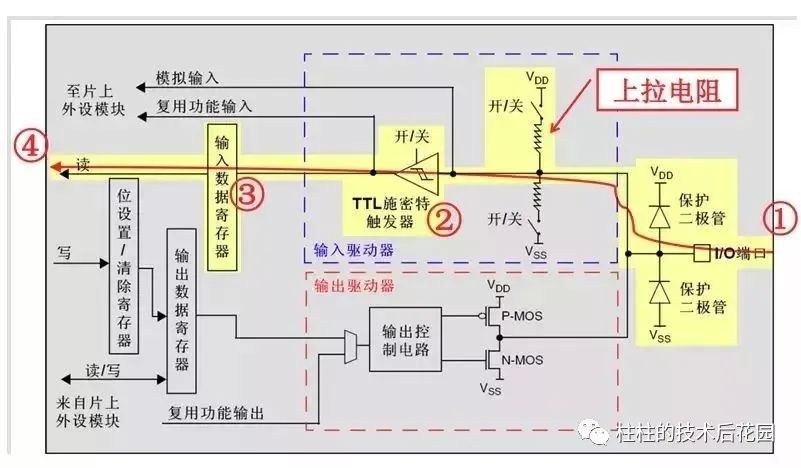

3.1.2 上拉輸入

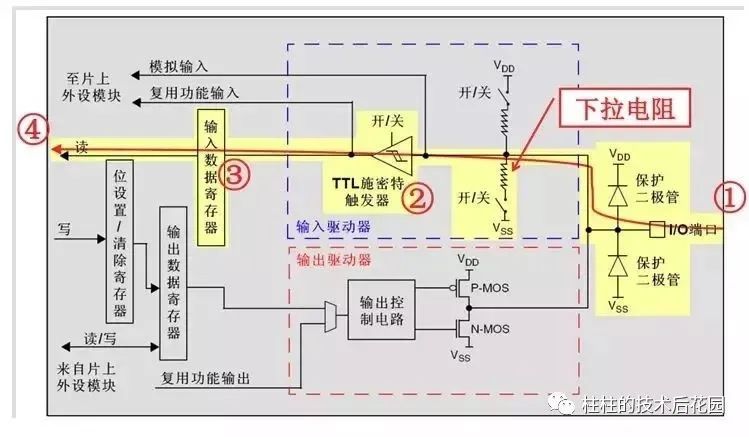

3.1.3 下拉輸入

下拉輸入模式下,I/O端口的電平信號直接進入輸入數據寄存器。但是在I/O端口懸空(在無信號輸入)的情況下,輸入端的電平可以保持在低電平;并且在I/O端口輸入為高電平的時候,輸入端的電平也還是高電平。

3.1.4 模擬輸入

模擬輸入模式下,I/O端口的模擬信號(電壓信號,而非電平信號)直接模擬輸入到片上外設模塊,比如ADC模塊等等。

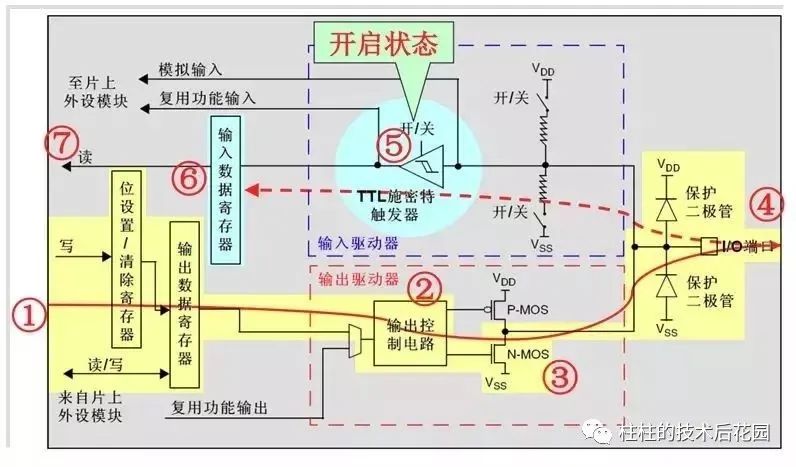

3.2 輸出模式

3.2.1 開漏輸出

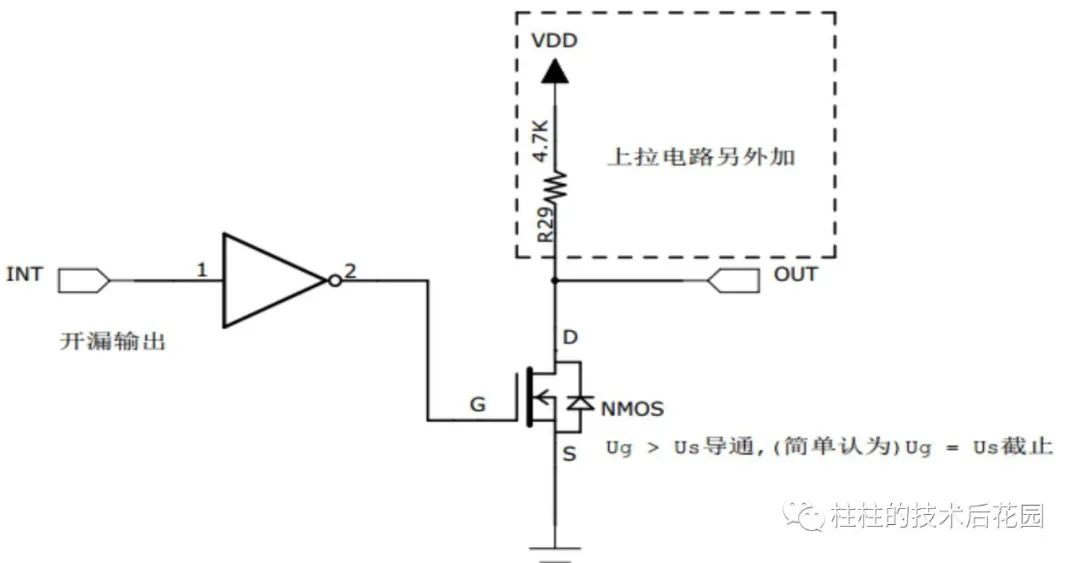

開漏輸出模式下,通過設置位設置/清除寄存器或者輸出數據寄存器的值,途經N-MOS管,最終輸出到I/O端口。

這里要注意N-MOS管,當設置輸出的值為高電平的時候,N-MOS管處于關閉狀態,此時I/O端口的電平就不會由前面設置輸出的高低電平決定,而是由I/O端口外部的上拉或者下拉決定;

當設置輸出的值為低電平的時候,N-MOS管處于開啟狀態,此時I/O端口的電平就是低電平。同時,I/O端口的電平也可以通過輸入電路進行讀取;

注意,讀取到的I/O端口的電平不一定是設置的輸出電平。

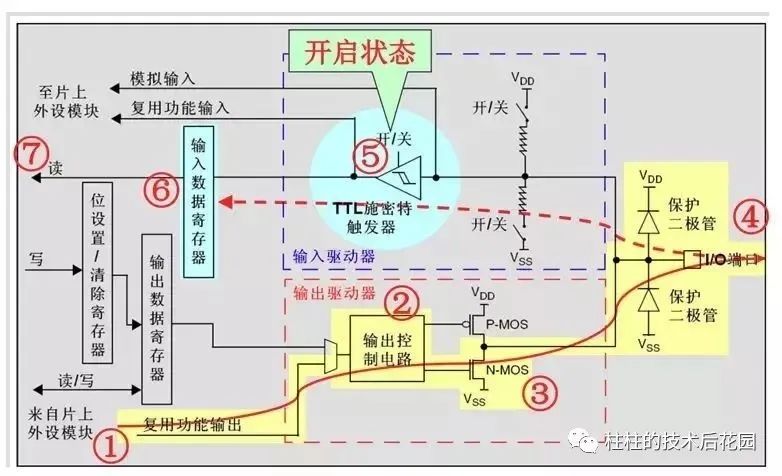

3.2.2 開漏復用功能

開漏復用輸出模式,與開漏輸出模式很是類似。只是輸出的高低電平的來源,不是讓CPU直接寫輸出數據寄存器,取而代之利用片上外設模塊的復用功能輸出來決定的。

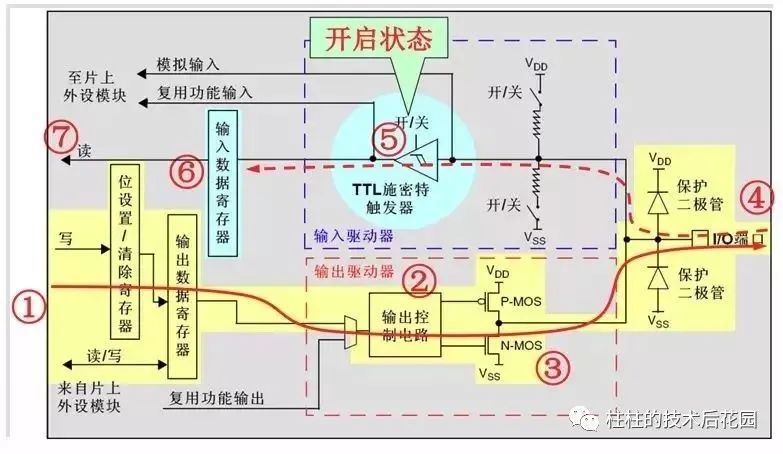

3.2.3 推挽式輸出

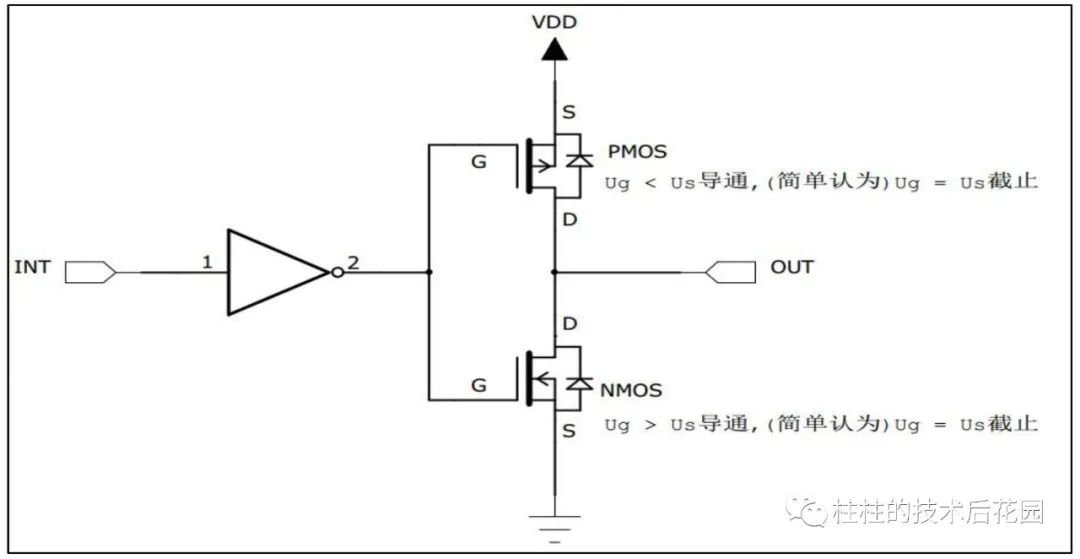

推挽輸出模式下,通過設置位設置/清除寄存器或者輸出數據寄存器的值,途經P-MOS管和N-MOS管,最終輸出到I/O端口。這里要注意P-MOS管和N-MOS管。

當設置輸出的值為高電平的時候,P-MOS管處于開啟狀態,N-MOS管處于關閉狀態,此時I/O端口的電平就由P-MOS管決定:高電平;

當設置輸出的值為低電平的時候,P-MOS管處于關閉狀態,N-MOS管處于開啟狀態,此時I/O端口的電平就由N-MOS管決定:低電平。同時,I/O端口的電平也可以通過輸入電路進行讀取;注意,此時I/O端口的電平一定是輸出的電平。

3.2.4 推挽式復用功能

推挽復用輸出模式,與推挽輸出模式很是類似。只是輸出的高低電平的來源,不是讓CPU直接寫輸出數據寄存器,取而代之利用片上外設模塊的復用功能輸出來決定的。

4 引申第三節詳細介紹了STM32F103ZET6的GPIO的八種工作模式,我們再引申闡述一下推挽輸出和開漏輸出的區別、開漏輸出的特點,以及“線與”的概念。

4.1 推挽輸出和開漏輸出的區別

推挽輸出等效電路圖

推挽輸出電路由兩個MOS管組成(上方的P-MOS和下方N-MOS),而開漏輸出則由上拉電阻和一個N-MOS管組成。推挽輸出的工作原理是:當需要輸出高電平時,上方P-MOS管導通,下方N-MOS管關閉。而若要輸出低電平時,下方的N-MOS管導通,上方的P-MOS管關閉。當引腳高低電平切換時,兩個MOS管輪流導通,一個負責灌電流,另一個負責拉電流,使得負載能力和開關速度都有很大的提高。

開漏輸出等效電路圖

開漏輸出的工作原理是:若要輸出低電平,則N-MOS管導通,輸出接地,輸出低電平。若要輸出高電平時,N-MOS管關閉,則既不輸出高電平又不輸出低電平,為高阻態。所以,需要外接上拉電阻,讓上拉電阻提供高電平的驅動能力。因為內部管腳為高阻狀態,所以,其具有“線與”特性,即將多個開漏極直接直接相連,只有所有的開漏極都是高阻狀態,輸出才為高電平,否則,為低電平。

4.2 開漏輸出的特點

開漏形式的電路有以下幾個特點:

1. 利用外部電路的驅動能力,減少IC內部的驅動。當IC內部MOSFET導通時,驅動電流是從外部的VCC流經Rpull-up ,MOSFET到GND。IC內部僅需很小的柵極驅動電流。

2. 一般來說,開漏是用來連接不同電平的器件,匹配電平用的,因為開漏引腳不連接外部的上拉電阻時,只能輸出低電平,如果需要同時具備輸出高電平的功能,則需要接上拉電阻,很好的一個優點是通過改變上拉電源的電壓,便可以改變傳輸電平。比如加上上拉電阻就可以提供TTL/CMOS電平輸出等。(上拉電阻的阻 決定了邏輯電平轉換的沿的速度 。阻 越大,速度越低功耗越小,所以負載電阻的選擇要兼顧功耗和速度)。

3. OPEN-DRAIN提供了靈活的輸出方式,但是也有其弱點,就是帶來上升沿的延時。因為上升沿是通過外接上拉無源電阻對負載充電,所以當電阻選擇小時延時就小,但功耗大;反之延時大功耗小。所以如果對延時有要求,則建議用下降沿輸出。

4. 可以將多個開漏輸出的Pin,連接到一條線上。通過一只上拉電阻,在不增加任何器件的情況下,形成“與邏輯”關系。這也是I2C、SMBus等總線判斷總線占用狀態的原理。

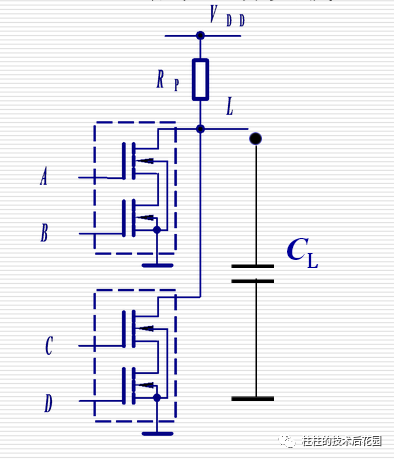

4.3 “線與”

在一個結點(線)上, 連接一個上拉電阻到電源 VCC 和 n 個 NPN 的集電極C 或 NMOS晶體管的漏極D, 這些晶體管的****極E或源極S都接到地線上,只要有一個晶體管飽和, 這個結點(線)就被拉到地線電平上。

因為這些晶體管的基極注入電流(NPN)或柵極加上高電平(NMOS),晶體管就會飽和, 所以這些基極或柵極對這個結點(線)的關系是或非 NOR 邏輯. 如果這個結點后面加一個反相器, 就是或 OR 邏輯。

其實可以簡單地理解為:在所有引腳連在一起時,外接一上拉電阻,如果有一個引腳輸出為邏輯0,相當于接地,與之并聯的回路“相當于被一根導線短路”,所以外電路邏輯電平便為0,只有都為高電平時,與的結果才為邏輯1。

*博客內容為網友個人發布,僅代表博主個人觀點,如有侵權請聯系工作人員刪除。