向Linux看齊,立志存活三十年:包云崗團隊開源高性能RISC-V處理器「香山」

中國科學院計算技術研究所的包云崗團隊推出了一款開源的高性能 RISC-V 處理器——香山。他們給自己定的小目標是:存活 30 年。

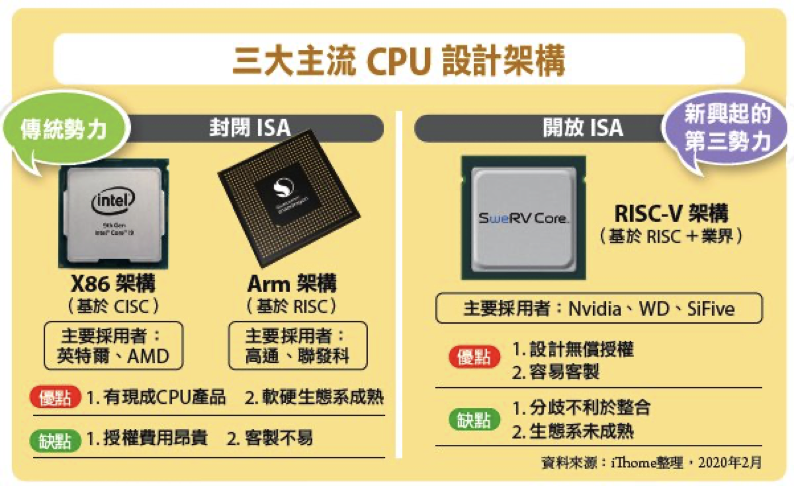

在 CPU 架構領域,Arm 和 X86 分別在移動端和桌面端占據了絕大部分市場份額。但是,這兩個巨頭對指令集的授權管控極為嚴格,這意味著大多數芯片企業只能購買其半成品或接近成品的技術,在其基礎上進行相對邊緣化的研發,沒有機會掌握真正核心、底層的技術。少數實力雄厚的企業能取得授權,也要付出數千萬甚至上億美元的授權費代價[1]。這使得越來越多的芯片研發企業轉向了開源的 RISC-V。

加州大學伯克利分校教授、RISC-V 發明人 David Patterson 曾大膽預言:「在五到十年內,RISC-V 可能成為世界上最重要的指令集」。

隨著 RISC-V 熱度不斷上升,這一預言似乎正逐漸走向現實。

前段時間,路透社等外媒報道稱,英特爾正計劃以 20 億美元的價格收購全球首家基于 RISC-V 架構的半導體初創公司 SiFive。去年剛從英特爾離職的半導體行業大牛 Jim Keller 也透露出了對 RISC-V 前景的樂觀,他表示,「這是一個非常好的指令集。(與 Arm 和 x86 相比,)它是最簡單的一個,擁有所有該有的功能,而且沒有太多垃圾。如果我想要快速構建一臺計算機,并且希望它運行得夠快,那么 RISC-V 是最容易的選擇。」

放眼國內,RISC-V 的熱度也在不斷上漲。6 月 21 日,第一屆 RISC-V 中國峰會在上海科技大學拉開帷幕。在本屆峰會上,中國科學院計算技術研究所研究員、中國開放指令生態(RISC-V)聯盟秘書長包云崗介紹了他們團隊最近開發的一款開源高性能 RISC-V 處理器——香山。

開源鏈接:https://github.com/OpenXiangShan/XiangShan (除了 GitHub,國內幾個開源平臺 Gitee/Trustie/iHub 上都有「香山」的鏡像,搜「XiangShan」就能找到。)

為什么要做「香山」?此前,包云崗團隊發現,Linux誕生30年,其不僅被工業界廣泛應用,也成為學術界開展操作系統研究的創新平臺,而CPU領域尚未產生一個類似的開源主線。

「要建立一個像Linux那樣的開源RISC-V核主線,既能被工業界廣泛應用,又能支持學術界試驗創新想法。最關鍵的是,一定要讓它像Linux那樣至少存活30年。」這是「香山」團隊給自己定下的小目標。

「我們做了一年多的準備工作——申請經費,啟動『一生一芯』計劃培養人才,建立團隊,尋找合作伙伴……終于,香山正式啟動了。」

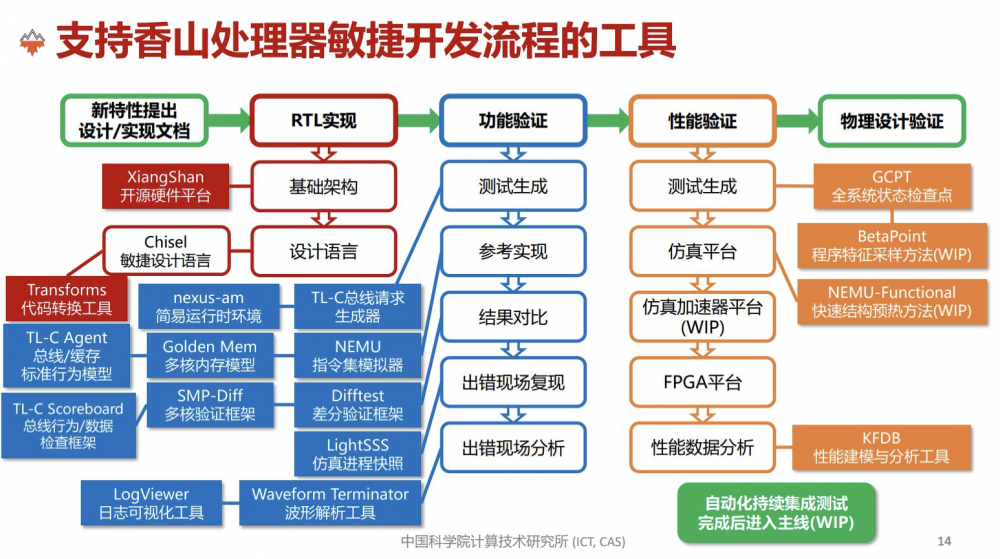

據悉,「香山」的理念是代碼開源、流程開放、文檔公開[2]。它基于 Chisel 硬件設計語言實現,支持 RV64GC 指令集。在「香山」處理器的開發過程中,團隊使用了包括 Chisel、Verilator 等在內的大量開源工具,實現了差分驗證、仿真快照、RISC-V 檢查點等處理器開發的基礎工具,建立起了一套包含設計、實現、驗證等在內的基于開源工具的處理器前端敏捷開發流程。其開源許可證采用的是木蘭寬松許可證。[3]

目前,「香山」共有兩版微架構,第一版叫「雁棲湖」,第二版叫「南湖」。

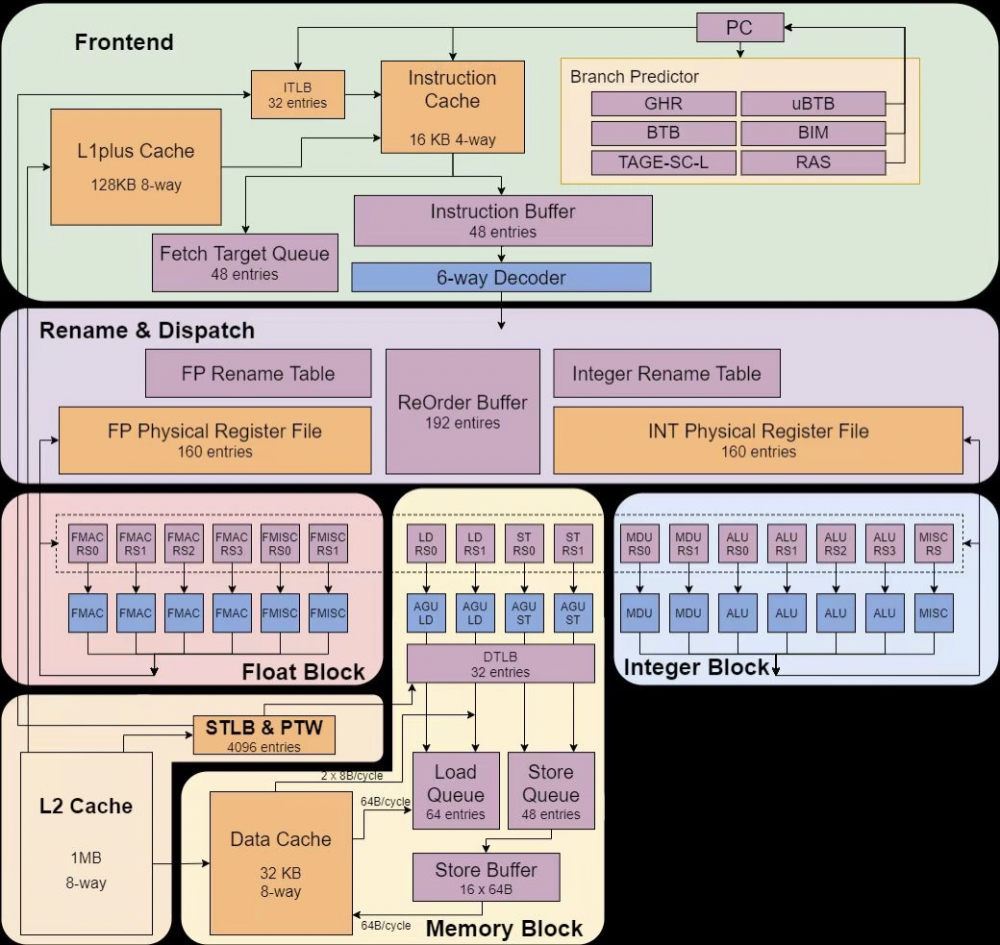

「雁棲湖」是一個11級流水、6****、4個訪存部件的亂序處理器核。它的開發始于 2020 年 6 月,RTL 于今年 4 月份完成。該架構的頻率可以達到 1.3GHz@TSMC 28nm,性能預計可以達到 7 分 / GHz(SPEC CPU 2006)。

「雁棲湖」架構概覽。

在 RISC-V 中國峰會上,包云崗介紹了「雁棲湖」架構開發的幾個關鍵決策。

第一個決策是選擇使用 Chisel 語言(伯克利大學發布的一種開源硬件構建語言)。與使用傳統的 Verilog 語言相比,使用 Chisel 進行敏捷開發效率可以提升 13 倍,代碼量僅為傳統開發的 1/5,而且可以達到傳統開發的質量水平。

第二個決策是重視構建支持敏捷設計的流程與工具,包括效率接近 QEMU 的高性能解釋器 NEMU、TL-C 一致性 Cache 的軟件測試框架 Agent Faker、指令級在線差分驗證框架 Difftest、基于內存的輕量級仿真快照 LightSSS、填補底層波形和高層語義鴻溝的調試棧 Waveform Terminator、可以在 10 小時內估算出 RISC-V CPU SPEC 分數的 BetaPoint 等。這些工具加速了整個開發和驗證流程。

包云崗表示,「雁棲湖」將在 7 月中旬流片,未來目標是達到 ARM Cortex-A76 的性能水平。

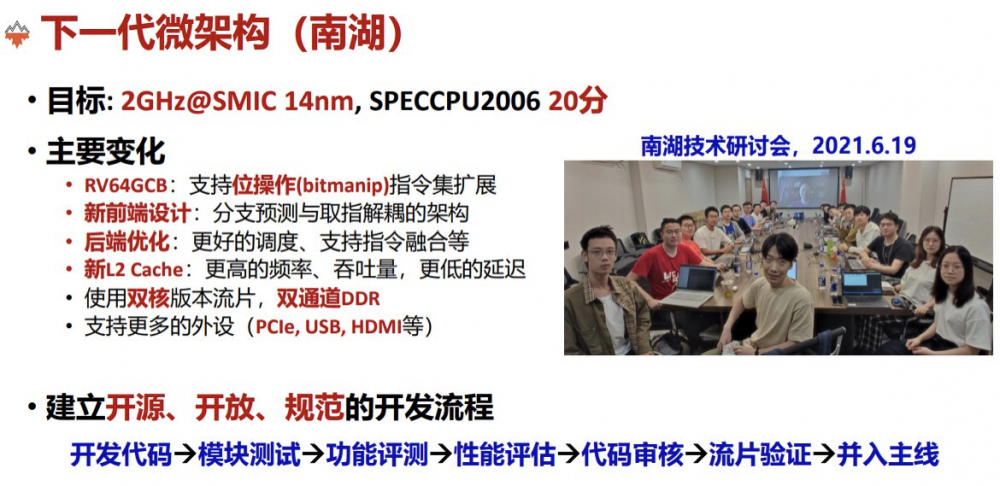

與「雁棲湖」相比,「南湖」的設計目標更高:頻率期望達到 2GHz@SMIC 14nm,性能期望達到 10 分 / GHz(SPEC CPU 2006 )。該版本的設計于今年 3 月份啟動,預計 2021 年底流片。

截至 2021 年 6 月 1 日,共有 25 位中科院計算所的同學 / 老師參與「香山」項目,他們貢獻了 31784 行香山核設計代碼和 18317 行驗證框架代碼。首期「一生一芯」計劃的五位同學(金越、王華強、王凱帆、張林雋、張紫飛)在本科一畢業便加入了香山的開發,成為了技術骨干。6 月 19 日,技術團隊在嘉興南湖召開了一場研討會。

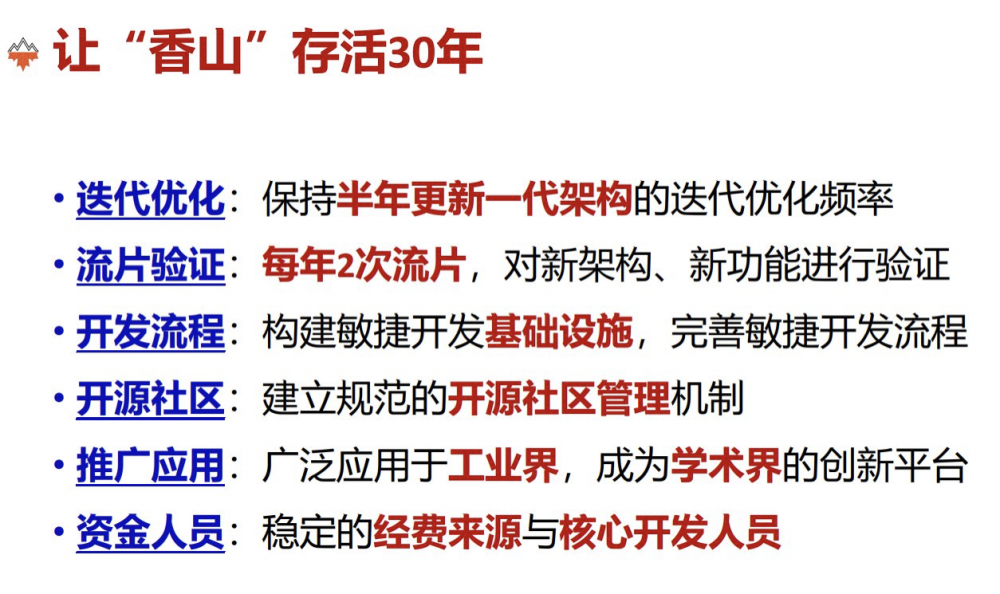

包云崗表示,為了建立像 Linux 這樣的被工業界廣泛應用的體系結構創新開源平臺,實現使香山存活 30 年的目標。為此,他們還有很多工作要做,包括保持半年更新一代架構的迭代優化頻率;每年 2 次流片,對新架構、新功能進行驗證等。

合作方面,北京微核芯科技為「香山」提供了第一期產業經驗、幫助完成了結構設計及物理設計。目前,項目的第二期正在招募聯合開發合作伙伴,已經加入的企業包括微核芯、字節跳動、北京奕斯偉、優矽科技等。包云崗表示,「這些來自工業界的積極反饋,讓我們更堅定地去踐行科研重工業模式。」(科研重工業模式即熱衷于研制真正能改變現狀的原型系統,哪怕需要大量工程投入,典型代表是加州大學伯克利分校。[4])

從「香山」的發布和產業支持不難看出,國內半導體行業對 RISC-V 的熱情也在持續高漲。但不可否認的是,該指令集的生態構建還需要一段時間。在前段時間的一次采訪中,包云崗坦言,采用 RISC-V 實現復雜場景下需求的應用還在起步初期,要想走進生態豐富且穩固的服務器、電腦、手機等傳統領域,還有很長一段路要走。他粗估,至少要 5 年至 10 年[1]。

也有人認為,因為足夠開放,RISC-V 的生態弱項未來有可能反轉成優勢。「產業的生態環境還在形成,沒有老牌霸主,我們有機會打造包括指令集、核心芯片、操作系統,以及上層應用、云服務在內的可控生態。」華米科技創始人黃汪表示[1]。

當然,生態的建設不是一件容易的事。「對于 RISC-V 來說,如何讓參與進來的玩家形成合力是一個挑戰。」阿里巴巴平頭哥市場部負責人高慧指出,過去 ARM 和 X86 這些指令集都有一個核心玩家,推動指令集不斷向某一個方向演進。現在,開源開放的 RISC-V 吸引了很多玩家,需要思考如何形成合力,而不是分叉發展[1]。

其實,這也是「香山」項目的初衷之一,即「形成『競爭前合作』,實現各界聯合開發開源 CPU 架構」。只有加強合作,RISC-V 生態才能早日發展壯大。

參考鏈接:

[1] https://baijiahao.baidu.com/s?id=1696983669207732243&wfr=spider&for=pc

[2] https://www.zhihu.com/question/466393646/answer/1955410750

[3] https://openxiangshan.github.io/

[4] https://zhuanlan.zhihu.com/p/268197755

*博客內容為網友個人發布,僅代表博主個人觀點,如有侵權請聯系工作人員刪除。