深亞微米時代,傳統材料、結構乃至工藝都在趨于極限狀態,摩爾定律也已有些捉襟見肘。而步入深亞納米時代,晶體管的尺寸就將接近單個原子,無法再往下縮減。傳統ASIC和ASSP設計不可避免地遭遇了諸如設計流程復雜、生產良率降低、設計周期過長,研發制造費用劇增等難題,從某種程度上大大放緩了摩爾定律的延續。

顯而易見的是,在巨額的流片成本面前,很多中小規模公司不得不改變策略,更多的轉向FPGA的開發和設計。反觀FPGA市場,即便是5年前,其相對于ASIC的市場增速還是相當遲緩的,但在近些年,尤其是邁進90n

關鍵字:

FPGA CPU

All Programmable 技術和器件的全球領先企業賽靈思公司(Xilinx, Inc. (NASDAQ:XLNX))今天宣布,Vivado®設計套件開始支持包括Zynq® UltraScale+和Kintex® UltraScale+器件在內的16nm UltraScale™+產品組合的早期試用。該Vivado早期試用版工具已與UltraScale+ ASIC級可編程邏輯進行了協同優化,能夠充分發揮量產級UltraScale+器件的優勢,進而利用整個目錄中的

關鍵字:

Xilinx Vivado

賽靈思公司(Xilinx)宣布加入工業互聯網聯盟(Industrial Internet Consortium,IIC),共同協作推動工業物聯網(IIoT)通用架構和框架。面向IIoT系統,賽靈思AllProgrammable標準型解決方案融軟件可編程功能、實時處理、硬件優化和兼具保密性與安全性的任意互連功能為一體。工業互聯網聯盟于2014年由AT&T、思科(Cisco)、通用電氣(General Electric)、IBM和英特爾(Intel)共同創立,致力于加速并協調各種優先發展事項,并加

關鍵字:

Xilinx 工業互聯網

Altera宣布將主辦2015年Altera技術大會(Altera Technology Day,ATD)活動,這是橫跨亞太地區八個地點的一系列以技術為導向的研討會,包括臺灣、印度、新加坡、馬來西亞、韓國與中國,時間將從2015年8月6日至9月23日。

Altera技術及市場專家將會分享在電子系統設計上的最新趨勢, Terasic、MathWorks與Tektronix等合作夥伴也將展示在電子設計與產品上使用Altera的FPGA、SoC、IP與電源解決方案,以提供加速產品上市的價值。關于研討會

關鍵字:

Altera FPGA

All Programmable技術和器件的全球領先企業賽靈思公司(Xilinx, Inc. (NASDAQ:XLNX))今天宣布推出正式版(Public Access Release)SDSoC™開發環境,將Zynq® SoC和MPSoC用戶擴展至廣泛的系統和軟件工程師社群。SDSoC開發環境是賽靈思SDx™軟件定義開發環境系列成員之一,包括擴展庫、開發板、設計服務生態系統支持,可實現嵌入式C/C++語言應用開發。該SDSoC™開發環境正式版還強化了集成設

關鍵字:

Xilinx SDSoC

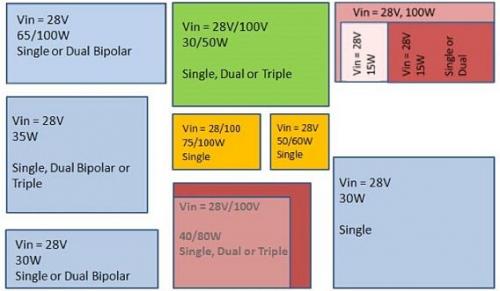

最近,航天子系統采用的先進半導體最底限是需有多個低電壓、具高電流軌條件,例如核心電壓小于1伏特(V)/30安培(A)的現場可編程門陣列(FPGA)。此外,各個負載也須具有獨特的排序、暫瞬、線路與負載調節的要求,這樣會讓配電網絡的設計變得更復雜。

目前航天總線提供28和100伏特不穩定的電源軌,可用于為最新的航天級半導體生成隔離的、有效率的穩壓電源。為滿足未來航天子系統的需求,開發一個低成本、可擴展的配電架構,且可重復的設計是尋求從28或100伏特兩種輸入中,可有效地生成多個較小的電軌,并同時限制

關鍵字:

FPGA PCB

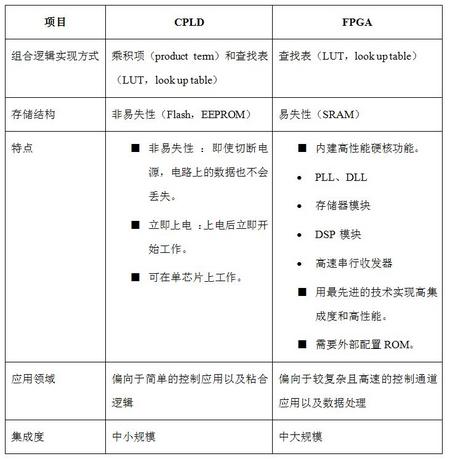

盡管很多人聽說過FPGA和CPLD,但是關于FPGA與CPLD之間的區別,了解的人可能不是很多。雖然FPGA與CPLD都是“可反復編程的邏輯器件”,但是在技術上卻有一些差異。簡單地說,FPGA就是將CPLD的電路規模、功能、性能等方面強化之后的產物。(特權同學版權所有)

一般而言, FPGA與CPLD之間的區別如表1.1所示。(特權同學版權所有)

表1.1 FPGA和CPLD的比較

?

總而言之,FPGA和CPLD最大的區別是他們的存儲

關鍵字:

FPGA CPLD

當前對于各種加密算法。除了有針對性的破解算法,最基本的思想就是窮舉密鑰進行匹配,通常稱為暴力破解算法。由于暴力破解算法包含密鑰個數較多,遍歷的時間超過實際可接受的范圍。如果計算速度提高到足夠快。這種遍歷的算法因結構設計簡便而具有實際應用的前景。

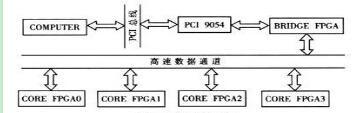

PCI總線(外設互聯總線)與傳統的總線標準——ISA總線(工業標準結構總線)相比,具有更高的傳輸率(132MBps)、支持32位處理器及DMA和即插即用等優點,用于取代ISA總線而成為目前臺式計算機的事實I/O總線標準,在普通PC

關鍵字:

FPGA PCI

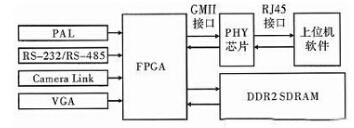

FPGA豐富的邏輯資源、充沛的I/O引腳以及較低的功耗,被廣泛應用于嵌入式系統和高速數據通信領域。現如今,各大FPGA生產廠商為方便用戶的設計和使用,提供了較多的、可利用的IP核資源,極大地減少了產品的開發周期和開發難度,從而使用戶得以更專注地構思各種各樣創意且實用的功能,而不是把大量時間浪費在產品的調試和驗證中。

千兆以太網技術在工程上的應用是當前的研究熱點之一。相比于其他RS-232或RS-485等串口通信,千兆以太網更加普及和通用,可以直接與Internet上的其他終端相連;相比于百兆網絡

關鍵字:

FPGA DDR2

因為硬件有了更多的模塊,及其解決方案,給人一種假象:硬件設計好像很簡單的一樣,實際呢,硬件設計才真正是考驗功底的。

關鍵字:

硬件設計 FPGA

Altera公司開發了基于其Arria® 10 SoC的存儲參考設計,與目前的NAND閃存相比,NAND閃存的使用壽命將加倍,程序擦除周期數增加了7倍。參考設計在經過優化的高性價比單片解決方案中包括了一片Arria 10 SoC和集成雙核ARM® Cortex®A9處理器,同時采用了Mobiveil的固態硬盤(SSD)控制器,以及NVMdurance的NAND優化軟件。這一參考設計提高了NAND應用的性能和靈活性,同時延長了數據中心設備的使用壽命,從而降低了NAND陣列的成本。

關鍵字:

Altera FPGA

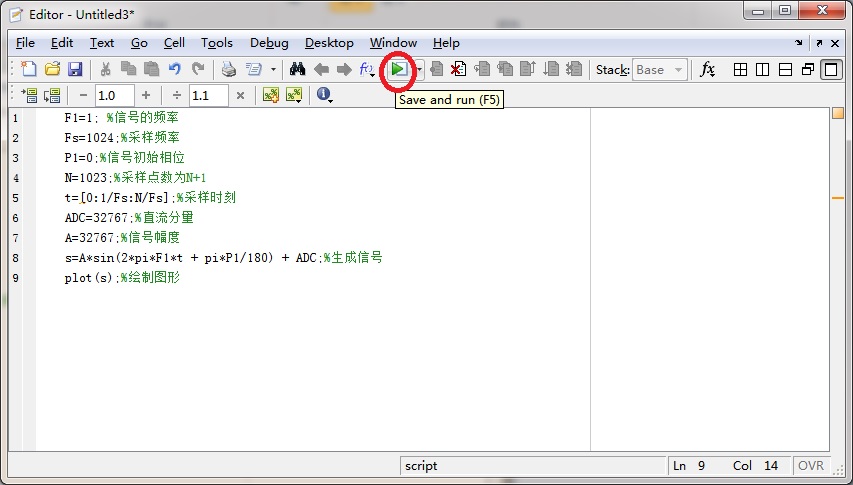

本文檔主要講解實現一個1024點的16位正弦波數據的生成,并將該數據制作成quartus II使用的mif文件,使用此文件,我們便可以使用FPGA,基于直接數字合成(DDS)原理生成標準的正弦波,即實現信號發生器的功能。小梅哥的DDS實驗已經做完,目前還沒有進行文檔的編寫。朋友今天邀請我為他制作一個1024點的16位的正弦波mif文件,實現之后,發現過程中涉及到MATLAB軟件、Excel軟件、Quartus II軟件的使用,每個過程簡單,但是步驟較多,因此在這里以文檔的方式記錄下來,分享給需要的朋友

關鍵字:

FPGA mif

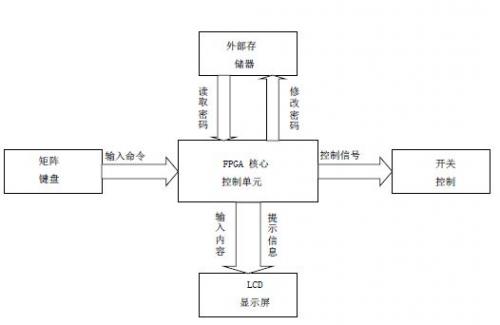

本文介紹了一種以FPGA為基礎的數字密碼鎖。采用自頂向下的數字系統設計方法,將數字密碼鎖系統分解為若干子系統,并且進一步細劃為若干模塊,然后用硬件描述語言VHDL來設計這些模塊,同時進行硬件測試。測試結果表明該數字密碼鎖能夠校驗10位十進制數字密碼,且可以預置密碼,設有斷電保護裝置,解碼有效指示等相應功能。

1功能概述

(1)密碼鎖的工作時鐘由外部晶振提供,時鐘頻率為50MHz,運算速度高,工作性能穩定。

(2)密碼的設置和輸入由外接鍵盤完成,控制電路的安全系數高,操作方便;

關鍵字:

FPGA 數字密碼鎖

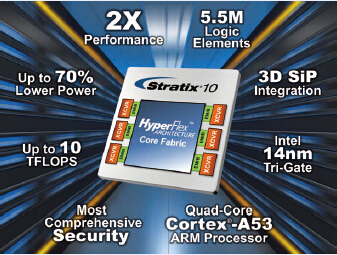

即將于2015年秋天提供Stratix 10 FPGA和SoC工程樣片的Altera公司,近日發布其Stratix 10 FPGA和SoC體系結構和產品細節,在性能、集成度、密度和安全特性方面實現了突破。 Stratix 10 FPGA和SoC采用了Altera革命性的HyperFlex FPGA架構,由Intel 14nm三柵極工藝技術制造,內核性能是前一代FPGA的2倍。性能好、密度高、具有先進的嵌入式處理功能的FPGA與GPU類浮點計算性能和異構3D SiP集成特性相結合,支持Altera客戶

關鍵字:

Stratix 10 FPGA SoC工程樣片 Altera 201507

賽靈思公司(NASDAQ:XLNX)今天宣布與中國移動研究院(CMRI)就下一代前傳接口(NGFI)的開發簽署合作備忘錄(MOU),雙方在中國移動研究院舉辦的NGFI研討會上舉行了隆重的簽約儀式。隨著5G寬帶多天線系統的出現,Xilinx和CMRI正結合C-RAN、大型天線系統和3DMIMO等新興技術,共同研究開發新型無線網絡前傳接口的關鍵技術和組件。

中國移動研究院首席科學家易芝玲博士表示“現在是時候重新考慮前傳解決方案了,這對解決CRAN部署所面臨的主要挑戰至關重要。我們正在努力

關鍵字:

Xilinx 5G

xilinx fpga介紹

Xilinx FPGA

Xilinx FPGA主要分為兩大類,一種側重低成本應用,容量中等,性能可以滿足一般的邏輯設計要求,如Spartan系列;還有一種側重于高性能應用,容量大,性能能滿足各類高端應用,如Virtex系列,用戶可以根據自己實際應用要求進行選擇。 在性能可以滿足的情況下,優先選擇低成本器件。

Xilinx FPGA可編程邏輯解決方案縮短了電子設備制造商開發產品的時間 [

查看詳細 ]

關于我們 -

廣告服務 -

企業會員服務 -

網站地圖 -

聯系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網安備11010802012473