基于千兆網的FPGA多通道數據采集系統設計

FPGA豐富的邏輯資源、充沛的I/O引腳以及較低的功耗,被廣泛應用于嵌入式系統和高速數據通信領域。現如今,各大FPGA生產廠商為方便用戶的設計和使用,提供了較多的、可利用的IP核資源,極大地減少了產品的開發周期和開發難度,從而使用戶得以更專注地構思各種各樣創意且實用的功能,而不是把大量時間浪費在產品的調試和驗證中。

本文引用地址:http://www.104case.com/article/277032.htm千兆以太網技術在工程上的應用是當前的研究熱點之一。相比于其他RS-232或RS-485等串口通信,千兆以太網更加普及和通用,可以直接與Internet上的其他終端相連;相比于百兆網絡,千兆以太網傳輸速度更快、傳輸距離更遠,再結合UDP/IP協議棧,可以更方便地與上位機進行通信。

本文結合FPGA和千兆以太網靈活與快速的優勢,設計了一個多通道并支持不同格式的數據采集系統。為了更好地為上位機軟件所支持,搭建了一個簡單的UDP/IP數據通道來完成數據到上位機的高速傳輸。同時,為了克服UDP這類不可靠的、面向無連接的協議帶來的數據錯誤和缺失問題,使用一塊DDR2SDRAM芯片來緩存各通道數據,在應用層制定了與上位機交互及丟包處理的通信協議,從而保證了采集數據到達上位機的可靠性。

1系統總體結構

系統的設計目標是為了讓不同通道、不同格式的數據都能通過同一個網絡通道被快速無誤地傳遞給上位機,由于設備與上位機運行狀態的不同,采集數據速率的變化,甚至網線質量,使傳輸過程中的錯誤和丟包情況在所難免,所以需要有適當的機制和存儲器緩存來保證傳輸的可靠性。

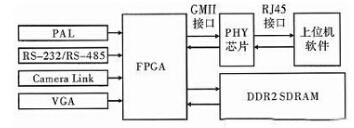

圖1 系統總體結構

圖1所示即為本系統的總體結構,除了使用一塊DDR2 SDRAM芯片之外,網絡模型中物理層的功能由一塊PHY芯片來完成。目前一般PHY芯片均能兼容10Mbit.s-1、100Mbit.s-1、1 000 Mbit.s-13種速率的以太網傳輸,并向上層提供多種接口,如MII、GMII、RGMII和TBI接口等,對于上位機一側則直接是普通的RJ45網口插槽。物理層接收數據鏈路層的并行數據,并將其轉換為原始的比特流;同時也將原始比特流轉化成并行數據,提交給數據鏈路層。

2 FPGA模塊功能

FPGA模塊通過響應上位機的指令,完成數據采集、打包、傳輸、丟包重傳等工作。所有工作的基礎是MAC子層、網絡層、傳輸層等OSI參考模型各層協議的可靠實現,每一層都按照標準接口向上一層提供特定服務,而把如何實現這些服務的細節對上一層加以屏蔽。

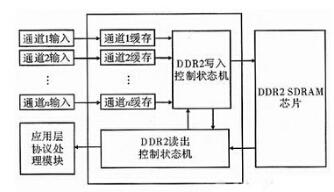

圖2 FPGA模塊結構

圖2顯示了系統FPGA模塊的具體結構,以及各個子模塊之間的關系。為縮短設計周期,提高設計質量,在模塊中分別調用了Altera公司現有的以太網控制器IP核和DDR2控制器IP核資源。

2.1 DDR2讀寫控制

若不考慮網絡中丟包的情況,數據一邊采集,一邊打包向上位機發送,是不需要外部存儲器來緩存的。但是在實際測試中發現,目前普通配置的PC機無法承受千兆以太網的快速傳輸能力,丟包很常見,尤其是增加到多個通道時,設備向上位機的輸出能力加大,丟包率也立即隨之升高。所以,使用一片DDR2 SDRAM緩存各通道的數據是必要的。

設計中直接調用Altera公司提供的DDR2 SDRAM控制器,并選用一塊它可以驅動的芯片來提高工作效率。芯片可使用的緩存空間是要重點關注的。每個通道都要分配固定的緩存區域,所以要將有限的內存空間作合理的劃分。如果是圖像數據,單個通道至少要有緩存兩幀以上的空間。DDR2讀寫控制模塊直接調用DDR2 SDRAM控制器IP核,但由于該IP核提供給用戶端的接口使用不方便,需要按照其文檔上介紹的時序來進行突發式讀寫。

本模塊的功能主要是協調各通道采集數據的寫入和讀出。如圖3所示,寫操作時,各通道的數據首先用FPGA資源進行緩存,然后寫入控制狀態機通過輪詢的方式依次檢查各個通道已經緩存的數據量,如果足夠一次突發寫,則將其寫入SDRAM芯片的相應通道塊中,然后再檢查下一通道;讀操作時,讀出控制狀態機也依次檢查各個通道寫入SDRAM芯片的數據量,如果足夠一次突發讀,則將其讀出,通過網絡發送出去。

圖3 DDR2 讀寫控制模塊結構

基于以上控制方式,設計對各通道的數據格式是不作限制,如圖1中所示,可以是PAL、Camera Link、VGA等各種格式的圖像或組合,只是在采集之前向上位機報告各個通道的數據信息。但需要說明的是,這些數據的帶寬總和理論上不應超過千兆以太網的最大傳輸速率,這是采用輪詢方式得以成功的前提。其實,如今普通PC機的處理能力遠遠不能達到這個最大限制,當速度到達100 Mbit.s-1時,上位機丟包就已經很嚴重。如果是將采集的數據在上位機上顯示,最多可能只有70~80 Mbit.s-1;如果還要將數據寫入硬盤,那數據率則會更低,除了配備一塊上好的硬盤之外,還需要在上位機軟件的優化上多作努力。

2.2以太網發送接收控制

本模塊的功能就是MAC子層、網絡層、傳輸層各層協議的具體實現,這些子模塊作為數據傳輸的通道,需要具有一定的緩存和查錯能力,同時為了能擴展其他協議,還必須保持相互之間的獨立性。如圖4所示,硬件設備接收數據的過程就是以太網幀經過每一層,去除各層的首部并核對校驗,最后獲得純粹的用戶數據;發送數據的過程就是用戶數據每經過一層,添加相應的首部和校驗,直到組成一個完整的以太網幀。

1)MAC子層的功能。設計中直接調用Altera公司提供的三速以太網控制器IP核實現MAC子層的功能,該IP核提供了統一的寄存器接口,用戶可以通過它來配置以太網最大幀長、源MAC地址、目的MAC地址和PHY地址等重要信息。如圖4所示,發送數據時,MAC模塊向數據幀添加以太網首部,并利用CRC算法添加32位的校驗碼;接收數據時,MAC模塊同樣要進行CRC校驗,對于不正確的數據幀要予以丟棄,用戶也可以通過配置寄存器決定是否將校驗位一并送至上一層。

(2)UDP/IP協議棧的實現。相對于TCP協議的三次握手,UDP和IP協議面向無連接的性質使其在硬件上可以快速實現,至于連接的建立完全可以在應用層實現。

如圖4所示,UDP和IP協議的功能在硬件上的實現有較多相同之處:對于上層發送的數據均需要添加相應的首部和校驗和;對于下層接收的數據,檢驗校驗和,并去除首部,然后才能送到上一層;由于首部中有該數據包的長度區域,所以無論是發送和接收,都需要將數據包全部緩存,才能確定其長度大小,相當于一種“存儲-轉發”的機制。

當然,UDP協議與IP協議在實現時也有不同的地方,主要體現在校驗和的計算方法上。UDP協議的校驗和是將首部和數據一起校驗,而且這個首部不僅是8 Byte的UDP首部,還包括12Byte的偽首部。在UDP層計算校驗和還用到了IP層的地址,但這違背了網絡分層模型的理念。IP協議的校驗和只計算IP數據包的頭部,一般情況下只有固定的20 Byte.

2.3應用層協議處理

不同通道采集的數據按照規定的數據包長度進行打包,然后再發送到上面的以太網控制模塊,需要專門的模塊進行組織和調度,并添加對應通道的標簽。同時,網絡中也不只是設備到上位機方向的采集數據包,也有反方向的用于控制的命令包:首先要考慮的問題是設備從何時開始采集數據,何時停止采集,這都是要上位機發送命令來控制的;其次,對于丟失包的統計與處理,這一部分工作稍微有些困難,但無論是設備和上位機都可以完成,顯然交給上位機處理比較適宜,然后上位機向設備發送帶丟失包序號的短數據包,設備優先從DDR2緩存中找到該丟失的數據包,發往上位機。

系統中完成這些功能的模塊相當于一個位于UDP/IP層之上的應用層協議,而這個協議的內容是由系統設計者所規定的,但必須為FPGA開發人員和上位機軟件程序開發人員所共享,這樣在不同機器上的對應層就有了一個可以互相通信的對等體(Peer)。這樣制定應用層協議,不但增加了系統相關功能的保密性,還可以由開發人員自行裁剪應用層功能,靈活地協調軟硬件應該負責的細節,最后敲定最簡潔的實現方案。

fpga相關文章:fpga是什么

評論