usb ip 文章 最新資訊

USB Type-C 和 USB Power Delivery: 專為擴展功率范圍和電池供電型系統(tǒng)而設計

- USB Type-C??(USB-C?) 是一種業(yè)界通用連接器,支持通過單個接口傳輸數(shù)據(jù)和電力,適用于個人電子產(chǎn)品、汽車、工業(yè)和企業(yè)系統(tǒng)等應用。USB Power Delivery (PD) 是使用 USB-C 連接器來增加 USB-C 接口功能和特性的標準。直到最近,USB PD 3.0 規(guī)范才允許高達 100W(20V、5A)的功率雙向流動,此功率范圍現(xiàn)在稱為標準功率范圍 (SPR)。最新的 USB PD 3.1 規(guī)范通過 USB-C 電纜將功率范圍增加至 240W(48V、5A),此功率范

- 關(guān)鍵字: 電池供電 USB Type-C USB Power Delivery

英飛凌PAG2P-2S全新AI智能全方位超高密度65W USB-C PD充電器

- 2021 年5月份 USB-IF 協(xié)會正式發(fā)布 USB PD3.1規(guī)范 , 輸出電壓由原5V、9V、15V和20V新增28V、36V及48V三種固定電壓 , 最大功率由100W 擴展至240W.使原本USB PD 應用于手機、平板電腦或筆記型電腦供電 , 擴展攜帶式手工具、兩輪電動機車等應用 , USB PD 一統(tǒng)供電、輸出線材標準 , 以減少電子垃圾產(chǎn)生.為加速USB PD 3.1 規(guī)格普及,英飛凌推出全新XDP數(shù)位電源控制 IC系列 PAG2P-2S , 提供ACF架構(gòu)高整

- 關(guān)鍵字: 英飛凌 PAG2P-2S 超高密度 65W USB-C PD 充電器

Diodes公司推出USB Sink控制器為電池供電裝置提供多功能PD EPR解決方案

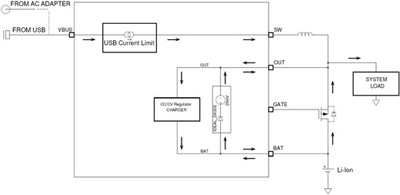

- Diodes 公司 (Diodes)近日推出兩款 USB Type-C? Power Delivery (PD) 3.1 擴展功率范圍 (EPR) Sink 控制器。這兩款控制器可以嵌入電池供電裝置和使用 USB Type-C 接口供電的設備中,包括路由器、無線揚聲器、移動電源和電動工具。AP33771C 和 AP33772S 器件可以幫助產(chǎn)品設計人員從專有充電端口、舊版 USB 端口和圓形插孔轉(zhuǎn)換到標準化的 USB PD 端口,同時讓他們能夠開發(fā)更小的產(chǎn)品應用,使用更少的元器件實現(xiàn)更快速充電。AP337

- 關(guān)鍵字: Diodes USB Sink控制器 電池供電 PD EPR

大聯(lián)大世平集團推出基于onsemi產(chǎn)品的240W USB PD充電器方案

- 近日,致力于亞太地區(qū)市場的國際領(lǐng)先半導體元器件分銷商---大聯(lián)大控股宣布,其旗下世平推出基于安森美(onsemi)NCP1680和NCP1345等芯片的240W USB PD充電器方案。圖示1-大聯(lián)大世平基于onsemi產(chǎn)品的240W USB PD充電器方案的展示板圖USB PD3.1協(xié)議的推出是快充領(lǐng)域的一項重大創(chuàng)新,其突破性地引入擴展功率范圍(EPR),新增28V、36V、48V三個電壓等級,并分別對應5A電流,將最大輸出功率提升至240W,這一升級預示著快充技術(shù)將不再僅局限于傳統(tǒng)手機、電腦等消費電子

- 關(guān)鍵字: 大聯(lián)大世平 onsemi USB PD充電器

智權(quán)半導體/SmartDV力助高速發(fā)展的中國RISC-V CPU IP廠商走上高質(zhì)量發(fā)展之道

- 進入2024年,全球RISC-V社群在技術(shù)和應用兩個方向上都在加快發(fā)展,中國國內(nèi)的RISC-V CPU IP提供商也在內(nèi)核性能和應用擴展方面取得突破。從幾周前在杭州舉行的2024年RISC-V中國峰會以及其他行業(yè)活動和廠商活動中,可以清楚地看到這一趨勢。作為全球領(lǐng)先的IP供應商,SmartDV也從其中國的客戶和志趣相投的RISC-V CPU IP供應商那里獲得了一些建議和垂詢,希望和我們建立伙伴關(guān)系攜手在AI時代共同推動芯片產(chǎn)業(yè)繼續(xù)高速發(fā)展。SmartDV也看到了這一新的浪潮。上一次在行業(yè)慶祝RISC-V

- 關(guān)鍵字: 智權(quán) SmartDV RISC-V CPU IP

聊聊USB

- 在人類的歷史長河中,很少有一種技術(shù)或者傳輸標準能像USB那樣跟我們的生活息息相關(guān),甚至到了沒有不行的地步。USB對于今天的人們來說,就好像是空氣,是水,是我們每天必需但是又熟視無睹的東西,沒有多少人知道它從哪來,也沒多少人關(guān)心它要往哪去,對于大多數(shù)人來說,它平凡得不能再平凡了。但是,在我們“電子攻城獅”的眼里,它太有趣了,它是目前使用率最高的接口,它是我們身邊林林總總電子設備之間的高速公路。因此我們必須關(guān)注它,如果有必要,我們還不得不去了解如何才能實現(xiàn)它。作為一個USB開發(fā)者(電子愛好者),接下來我會為大

- 關(guān)鍵字: USB 接口

引領(lǐng)充電新風尚:瑞薩以低成本實現(xiàn)100W/140W電源適配器方案

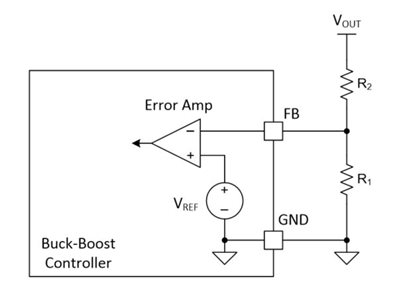

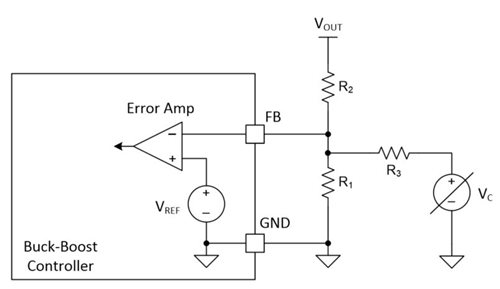

- 如今,移動設備已經(jīng)成為人們?nèi)粘I詈凸ぷ髦胁豢苫蛉钡拇嬖凇H欢S著設備種類和功能不斷擴展,其充電需求也變得日益復雜化和多樣化。在這種背景下,為突破傳統(tǒng)充電器在功率輸出、兼容性和便攜性等方面的挑戰(zhàn),USB-C和USB PD技術(shù)應運而生,它憑借出色的充電效率與小巧輕薄的外形,革新了電子設備的充電體驗。基于USB-C接口和USB PD技術(shù),瑞薩推出100W/140W電源適配器方案。該方案實現(xiàn)了低成本的單端口和雙端口USB-C和USB PD 3.1電源適配器設計,具有5-20V/5A 100W雙輸出或5-28V

- 關(guān)鍵字: USB PD 電源適配器

將ASIC IP核移植到FPGA上——如何確保性能與時序以完成充滿挑戰(zhàn)的任務!

- 本系列文章從數(shù)字芯片設計項目技術(shù)總監(jiān)的角度出發(fā),介紹了如何將芯片的產(chǎn)品定義與設計和驗證規(guī)劃進行結(jié)合,詳細講述了在FPGA上使用IP核來開發(fā)ASIC原型項目時,必須認真考慮的一些問題。文章從介紹使用預先定制功能即IP核的必要性開始,通過闡述開發(fā)ASIC原型設計時需要考慮到的IP核相關(guān)因素,用八個重要主題詳細分享了利用ASIC IP來在FPGA上開發(fā)原型驗證系統(tǒng)設計時需要考量的因素。在上篇文章中,我們分享了第二到第四主題,介紹了使用FPGA進行原型設計時需要立即想到哪些基本概念、在將專為ASIC技術(shù)而設計的I

- 關(guān)鍵字: ASIC IP FPGA SmartDV

Pulsiv發(fā)布了效率超高的65W USB-C設計,可將溫度降低30%,采用集成半有源橋,效率高達96%

- 位于英國劍橋的電力電子技術(shù)創(chuàng)新企業(yè)Pulsiv Limited宣布推出效率超高*的65W USB-C GaN優(yōu)化參考設計,該設計旨在解決電源中的復雜熱性能挑戰(zhàn)。這一備受期待的突破性開發(fā)成果將提供其他設計中所未有的獨特功能和優(yōu)勢組合,必將徹底改變USB-C快速充電領(lǐng)域。 PSV-RDAD-65USB參考設計將Pulsiv OSMIUM技術(shù)與行業(yè)標準的準諧振反激變換器和高度優(yōu)化、超緊湊的磁性組件相結(jié)合。它能大幅降低工作溫度、盡量減小損耗并縮小尺寸,引領(lǐng)了一系列突破功率轉(zhuǎn)換現(xiàn)有邊界的設計,旨在打造一個可持續(xù)的U

- 關(guān)鍵字: Pulsiv USB-C 半有源橋

新思科技推出業(yè)內(nèi)首款獲得ISO/SAE 21434網(wǎng)絡安全合規(guī)認證的IP產(chǎn)品,加速汽車安全領(lǐng)域發(fā)展

- 摘要:●? ?新思科技ARC HS4xFS處理器IP和新思科技IP開發(fā)流程均通過獨立審計機構(gòu)SGS-T?V Saar的ISO/SAE 21434認證。●? ?獲得ISO/SAE 21434認證可應對不斷變化的網(wǎng)絡安全威脅,有助于在整個生命周期內(nèi)為汽車系統(tǒng)提供長期的安全性與可靠性。●? ?經(jīng)過安全風險分析(SRA)認證的新思科技ARC HS4xFS處理器IP助力開發(fā)者能夠以安全的方式將IP集成到系統(tǒng)中,從而滿足ISO/SAE 21434要求。●&n

- 關(guān)鍵字: 新思科技 ISO/SAE 21434 網(wǎng)絡安全合規(guī)認證 IP 汽車安全

USB接口的EMC設計

- 在提到干擾對USB的影響時,差分數(shù)據(jù)傳輸與簡單的同軸電纜相比具有很大的優(yōu)勢。在感性干擾效應(磁場)情況下,導線的絞合可以彌補干擾效應。●USB控制器的輸入/輸出不是完全對稱的,因此USB信號顯示出共模干擾。●Layout與HF/EMC不兼容,寄生電容和缺少波阻匹配會產(chǎn)生共模干擾。●電路設計(USB濾波器)不充分,濾波器影響信號質(zhì)量,和/或插損太低。●接口設計(插座,外殼)不充分。不良的接地會減小電纜的屏蔽衰耗。濾波器具有不良的接地參考。●USB電纜不對稱、屏蔽不良以及沒有足夠好的接地。這種電纜會劣化信號質(zhì)

- 關(guān)鍵字: EMC 靜電測試 USB

將ASIC IP核移植到FPGA上——更新概念并推動改變以完成充滿挑戰(zhàn)的任務!

- 本系列文章從數(shù)字芯片設計項目技術(shù)總監(jiān)的角度出發(fā),介紹了如何將芯片的產(chǎn)品定義與設計和驗證規(guī)劃進行結(jié)合,詳細講述了在FPGA上使用IP核來開發(fā)ASIC原型項目時,必須認真考慮的一些問題。文章從介紹使用預先定制功能即IP核的必要性開始,通過闡述開發(fā)ASIC原型設計時需要考慮到的IP核相關(guān)因素,用八個重要主題詳細分享了利用ASIC所用IP來在FPGA上開發(fā)原型驗證系統(tǒng)設計時需要考量的因素。在上篇文章中,我們介紹了將ASIC IP移植到FPGA原型平臺上的必要性,并對原型設計中各種考量因素進行了總體概述,分析開發(fā)A

- 關(guān)鍵字: ASIC IP FPGA SmartDV

好玩的項目|使用微控制器 PIC16F1459 構(gòu)建 DIP 開關(guān) USB U盤

- 今天給大家分享我在github上看到的一個有意思的項目:使用微控制器 PIC16F1459 構(gòu)建 DIP 開關(guān) USB U盤。(附帶電路原理圖,PCB布局設計,原始應用程序。)主要是用撥片開關(guān)來進行配置設備,只需要撥動紅色開關(guān)就可以輕松配置文件。不需要編輯 XML 和 JSON 文件來存儲硬件或軟件的配置設置。這個項目分享給大家,步驟講解得很詳細,如果感興趣的可以動手試試。先放上成品圖。DIP 開關(guān)插電腦上圖DIP 開關(guān) U 盤的后視圖和前視圖(顏值還挺高的)一、元件選擇作者總共設計制作了兩種不同版本的D

- 關(guān)鍵字: MCU PIC16F1459 USB U盤

大聯(lián)大友尚集團推出基于ST產(chǎn)品的140W USB PD3.1快充方案

- 致力于亞太地區(qū)市場的國際領(lǐng)先半導體元器件分銷商—大聯(lián)大控股近日宣布,其旗下友尚推出基于意法半導體(ST)ST-ONEHP器件的140W USB PD3.1快充方案。圖示1—大聯(lián)大友尚基于ST產(chǎn)品的140W USB PD3.1快充方案的展示板圖近年來,快充行業(yè)不斷經(jīng)歷創(chuàng)新升級,每一次技術(shù)的躍進都為充電的效率與安全性帶來革命性變革。特別是USB PD3.1快充標準的引入,更是為該行業(yè)的發(fā)展樹立了新的里程碑。該標準不僅將最大充電功率提升至240W,同時新增多組固定和可調(diào)輸出電壓檔位,可為各種電子設備提供更加靈活

- 關(guān)鍵字: 友尚集團 ST 140W USB PD3.1 快充方案

燦芯半導體發(fā)布通用高性能小數(shù)分頻鎖相環(huán)IP及相關(guān)解決方案

- 一站式定制芯片及IP供應商——燦芯半導體(上海)股份有限公司近日宣布成功研發(fā)出一款通用高性能小數(shù)分頻鎖相環(huán)(fractional-N PLL) IP,支持24bits高精度小數(shù)分頻,最高輸出頻率4.5Ghz,另外還支持擴頻時鐘(SSC)功能,可以為客戶提供多功能的小數(shù)分頻 PLL解決方案。PLL電路一般用于產(chǎn)生輸出頻率,輸出頻率值與PLL的參考輸入頻率呈倍數(shù)關(guān)系。小數(shù)分頻PLL通過頻率乘法比例的小數(shù)值,實現(xiàn)更精確的輸出頻率控制,從而提供更高精度和準確度的輸出頻率。SSC發(fā)生器是在一定頻率范圍內(nèi)調(diào)制時鐘信號

- 關(guān)鍵字: 燦芯半導體 小數(shù)分頻 鎖相環(huán) IP

usb ip介紹

您好,目前還沒有人創(chuàng)建詞條usb ip!

歡迎您創(chuàng)建該詞條,闡述對usb ip的理解,并與今后在此搜索usb ip的朋友們分享。 創(chuàng)建詞條

歡迎您創(chuàng)建該詞條,闡述對usb ip的理解,并與今后在此搜索usb ip的朋友們分享。 創(chuàng)建詞條

關(guān)于我們 -

廣告服務 -

企業(yè)會員服務 -

網(wǎng)站地圖 -

聯(lián)系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產(chǎn)品世界》雜志社 版權(quán)所有 北京東曉國際技術(shù)信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產(chǎn)品世界》雜志社 版權(quán)所有 北京東曉國際技術(shù)信息咨詢有限公司